基于FPGA的等精度频率计的设计与实现

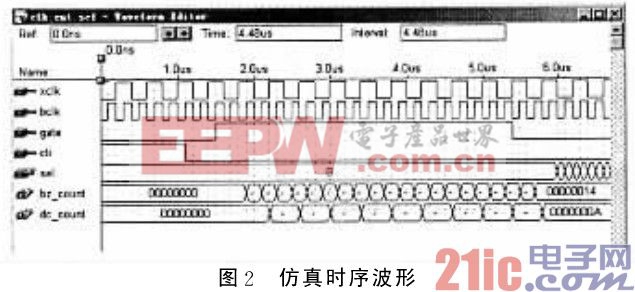

仿真波形如图2所示。

3 结 语

本文利用ALTERA公司的FPGA芯片EPF10K10,使用VHDL编程语言设计等精度频率计,给出核心程序,经过ISPEXPER仿真后,验证设计是成功的,达到预期结果。

和传统的频率计相比,FPGA的频率计简化了电路板的设计,提高了系统设计的实现性和可靠性,测频范围达到100 MHz,实现了数字系统硬件的软件化,这是数字逻辑设计的新趋势。

参考文献

[1]李景华,杜玉远.可编程逻辑器件与EDA技术[M].沈阳:东北大学出版社,2002.

[2]赵雅兴.FPGA原理、设计与应用[M].天津:天津大学出版社,1999.

[3]夏宇闻.复杂数字电路与系统的VERILOGHDL设计技术[M].北京:北京航空航天大学出版社,1998.

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码