基于STM32F417的图像采集系统设计

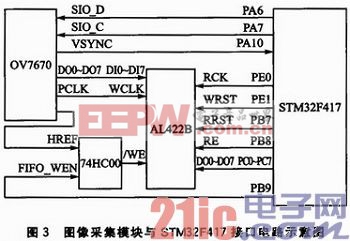

图像采集模块与STM32F417的接口电路示意图如图3所示。

在图3中,利用STM32F417的PC0~PC7口接收OV7670输出经过AL422B缓存后的8位图像数据。OV7670的SIO_D、SIO_C接口与STM32F417的PA6、PA7引脚相连,通过该接口实现对摄像头的初始化配置。STM32F417的PE0、PE1、PB7、PB8分别控制AL422B的时钟信号、写复位、读复位以及读使能信号。PB9与OV7670输出的行扫描信号通过与非芯片实现对帧缓存器写使能的控制,STM32F417的PA10引脚通过中断的方式检测摄像头是否输出一帧完整的图像。

由于OV7670带有标准SCCB接口,同时兼容I2C总线接口,本设计采用STM32F417产生的I2C总线信号模拟SCCB,实现对摄像头内部寄存器的初始化配置以及对其行场同步信号、开窗及输出格式的设置。对OV7670寄存器的配置方法如下:首先,发送OV7670的写地址0x42,然后发送写数据的目的寄存器地址和数据,从而初始化写操作;通过发送OV7670的读地址0x43,完成对读操作的初始化,从而实现对OV7670摄像头的初始化配置。

在对摄像头工作参数配置过程中,将OV7670的寄存器DBLV设为0x80,对输入时钟倍频数进行控制。设置寄存器BRIGHT、CONTRAS,控制图像的亮度和对比度。通过寄存器REG75、REG76设置图像边缘增强上、下限。在对摄像头测试阶段,首先将寄存器ACALING_YSC设为0x85,显示8色彩条,测试阶段结束后将该寄存器设为0x00,进入非测试模式。

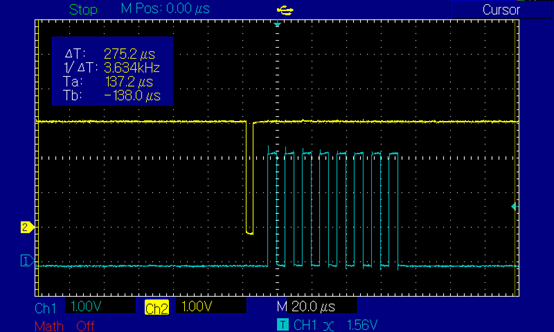

OV7670输出同步信号包括:场同步信号VSYNC、行同步信号HREF、像素时钟PCLK。根据OV7670数据手册提供的同步信号时序图可知,OV76 70摄像头的像素时钟PCLK与FIFO写时钟WCLK相连接,在PCLK有效时将数据写入FIFO。场同步信号VSYNC为扫描一帧图像定时,在两个正脉冲之间完成一帧图像的扫描。

当STM32F417第一次检测到VSYNC下降沿时,系统第一次产生中断,表明OV7670开始输出一帧图像,STM32F417将FIFO_WEN置高电平,当HREF有效(高电平)时,FIFO_WEN与HREF通过与非门使能FIFO的WCK,将有效图像数据自动写入FIFO中。

当第二次VSYNC中断产生时,表明已经将一帧完整的图像写入FIFO,系统通过将FIFO_WEN置低,锁存一帧图像数据,实现图像的静态存储。此时,STM32F417送给FIFO的读时钟RCLK一个上升沿,将数据从FIFO中读出来,完成图像数据的实时采集与提取。

1.7 存储模块

SD卡支持SPI和SD两种模式,本设计采用SPI模式,将SD卡的CMD引脚与SFM32F417的SPI3_MOSI相连,CLK连接STM32F417的SPI3_SCK引脚,DATA0连接STM32F417的SPI3_MISO引脚,DATA3作为片选CS与STM32F417的PA15相连;在SD卡收到复位命令时,若CS为有效电平则启动SPI模式,SD卡在SPI3_SCK的控制下通过DATA0完成数据的读写。

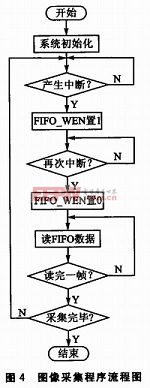

2 系统软件设计

在图像采集软件设计中,对系统各个部分的初始化是最为关键的一步,只有对各部分初始化成功以后,才能实现图像采集功能。图像采集初始化程序主要包括对系统、SCCB接口、OV7670摄像头、FIFO缓存器ALA22B等的初始化。在系统初始化设置成功以后,微控制器不断监测VSYNC信号电平变化,根据VSYNC产生的中断情况,控制FIFO对图像数据的读/写。图像采集程序流程图如图4所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码