智能公交电子站牌系统结构设计

②动态驱动方式

在横向一组像素的背电极并联在一起作为一个引脚引出,称之为行电极,在纵向一组像素的段电极并联在一起作为一个引脚引出,称之为列电极。这种结构构成了一个矩阵阵列,液晶屏上任一像素位置都能其所在的行与列唯一确定。液晶显示控制器在时序脉冲信号下,循环给行电极施加脉冲,同时给该行像素的所有列电极施加脉冲,使其实现所有显示像素的驱动,由于扫描循环周期很短,且是不断循环进行的,这样能够使液晶显示屏上呈现稳定的图像效果。

我们把这种扫描驱动方式称为动态驱。

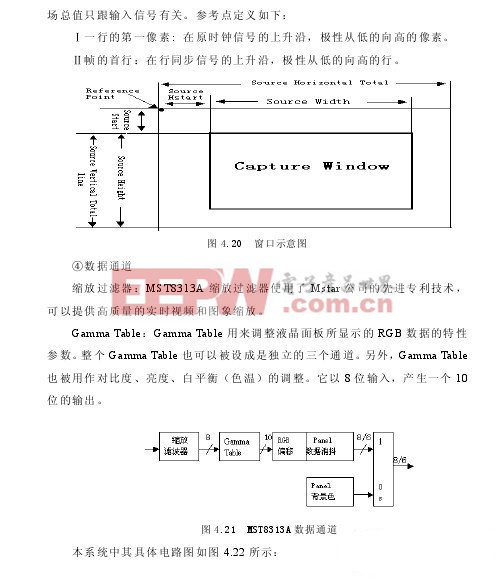

为了节省I/O口,减少大规模的驱动电路,本文中LCD屏采用动态驱动方式。ARM微处理器将图文信息转化为特定格式的点阵信息,将其存储在SDRAM存储器中,SCALER MST8131从SDRAM中接收信号,并转换为Panel可以识别的LVDS信号。

4.2.9显示系统中的信号处理

目前市面上面板分辨率越来越大,相应地信号频率也越来越高,电磁干扰成为一种必须克服的问题,LVDS信号以其在低电压和抗电磁干扰上的优势,受到大部分面板制造商的认可,因此LVDS接口在面板上的应用越来越普遍。

LVDS是一种差分信号技术,能有效控制电磁干扰,其低压与低电流驱动输出实现了低噪声和低功耗。

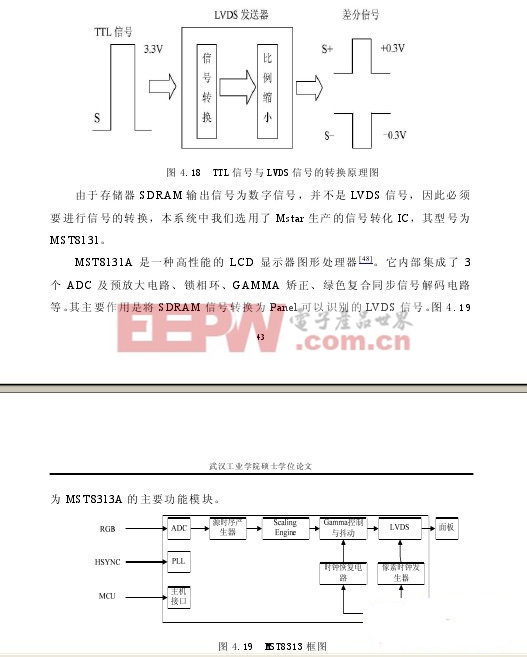

图4.18所示为TTL信号与LVDS信号的转换原理图,TTL信号经过信号转换后变为幅度一样而极性相反的两信号。通过一级电压比例衰减器后,可以将原来的高电压信号变为一对低电压信号,减少损耗。

①时钟恢复回路

MST8313有一个内部的时钟恢复回路,这个回路由一个数字时钟合成器和模拟电路PLL组成。它用来产生取样时钟信号,以采集模拟的RGB数据。这个回路锁定于输入的行同步信号,时钟恢复回路用来调整源时钟频率(SCLK);在每个行同步信号输入的上升沿产生反馈信号。包括第一个和最后一个行同步信号都可以产生60MHz的频率。在工作电压及温度要求的范围内,可以在1ms之内实现。

当面板的时钟信号与源时钟信号(或一半)不同时,有一个象素时钟用来驱动面板。它是由一个和时钟恢复回路一样的回路产生的。它们的区别在于:源时钟信号锁定于行同步输入信号,而目的时钟信号锁定于源时钟信号。

②模/数转换器

MST8313A内部集成了3个模/数转换器(ADC),每一色一个(R、G、B)。每个ADC都是8-bits输出,用于将输入的模拟RGB信号转换成8-bits的数字信号,分别为R0-R7、G0-G7、B0-B7。信号支持:MST8313A芯片支持数字分离信号、数字混合信号和模拟混合信号。支持所有的这些信号都不需要额外的外围电路。

③源时序产生器(STG)

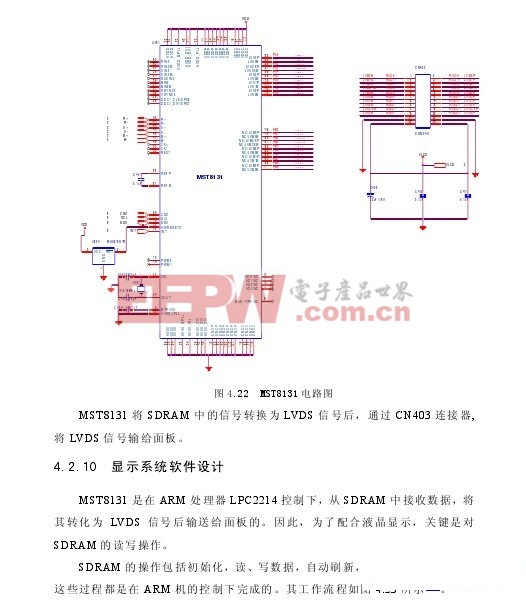

STG模块定义了一个图形抓取窗口,并且发送数据给数据通道模块。图

4.20显示了这个口的定义。

在水平的方向,它被定义在SCLKS(等价的像素计算);在纵向的方向,它被定义在行。所有以“Source”开头的参数均被定义在MST8313的寄存器中,

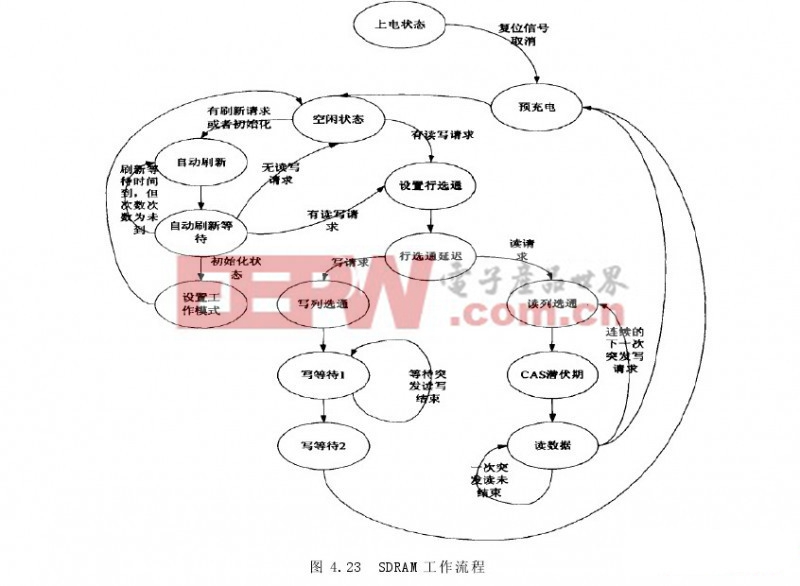

SDRAM在复位信号作用下将其状态驱动到上电状态后,微处理器将复位信号撤销,SDRAM进行一次预充电,对其相应的寄存器组、控制引脚信号进行配置。预充电完成后进入空闲状态,在该状态下,如果有刷新请求或者处于初始化阶段,则转入自动刷新状态,驱动相应的信号,启动刷新等待定时器。自动刷新后发出一个自动刷新应答信号,进入刷新等待状态,刷新等待定时器定时结束之后,结束本次刷新,之后再判断是否是初始化阶段,如果是初始化阶段,就要要进入工作模式设置状态,否则在无读写请求操作时回到空闲状态,有读写请求操作时转入行选通工作模式设置状态,行选通后会有一个时钟周期等待,进入列状态工作模式设置。如果此时是写请求,相应控制信号选通,同时置位突发使能信号,按照设定的突发长度操作,然后进入写等待状态,直到本次突发状态结束,然后进入第二个写等待状态进行缓冲,最后返回预充电状态;果是读请求,在列选通之后按照可编程长度进行列选通潜伏等待,然后SDRAM的数据会在数据端口连续的出现,进入等待读数据状态。读操作最后返回预充电状态。

4.3本章小结

本章节论述了电子站牌的硬件构成,分别给出了红外接收部分、无线通信部分以及显示部分的硬件电路图和软件设计,在本章中重点分析了电子站牌的动态显示部分,其电子站牌实图与武汉目前装配的类似,其信号传输方式与传输流程不同,再者就是我们采用LCD屏显示车辆信息,对比武汉目前装配的电子站牌,其车辆信息显示量要大很多。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码