利用Xilinx FPGA和存储器接口生成器简化存储器接口

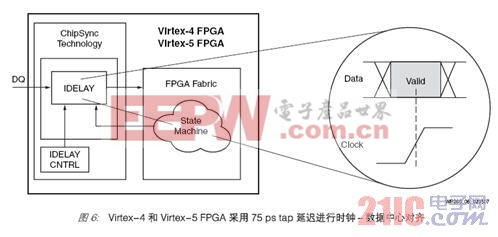

正如 Spartan-3 系列 FPGA 中所实现的那样,使用读数据 DQS 可以把读数据采集到可配置逻辑块 (CLB) 中,但是使用 LUT 把 DQS 或时钟与数据有效窗口中心对齐时,所用的延迟 tap 却很粗糙。CLB 中实现的延迟 tap 具有大约几百微微秒 (ps) 的分辨率,然而,对于超过 400 Mb/s 的数据速率的读取采集时序,所需的分辨率要比基于CLB 的 tap 高一个数量级。Virtex-4 和 Virtex-5 FPGA 采用 I/O 模块中的专用延迟和时钟资源(称为 ChipSync? 技术)来解决这一难题。内置到每个 I/O 中的 ChipSync模块都含有一串延迟单元(tap 延迟),在 Virtex-4 中称为 IDELAY,而在 Virtex-5FPGA 中称为 IODELAY,其分辨率为 75 ps (见图6)。

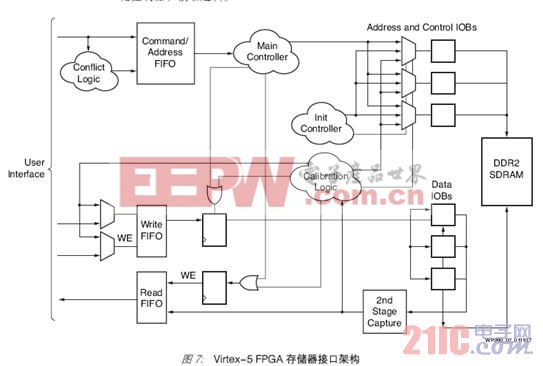

此实现的架构基于几个构建模块。用户界面负责把存储器控制器和物理层接口桥接到其余 FPGA 设计,它使用 FIFO 架构(图7)。FIFO 有三套:命令/ 地址 FIFO、写FIFO、读 FIFO。这些 FIFO 保存着命令、地址、写数据和读数据。主要的控制器模块控制读、写和刷新操作。其他两个逻辑模块执行读操作的时钟-数据中心对齐:初始化控制器和校准逻辑。

用于地址、控制和数据的物理层接口在 I/O 模块 (IOB) 中实现。读数据在锁存器的第二级(也是 IOB 的一部分)重新采集。

Virtex-4 和 Virtex-5 FPGA 存储器接口参考设计支持两种读数据采集技术。Virtex-4FPGA 支持的直接时钟技术延迟了读数据,因而使用 IOB 的输入 DDR 触发器中的系统时钟可直接寄存读数据。为将 FPGA 时钟对齐到最佳状态,对每个读数据位都会单独进行校验。这种技术为高达 240 MHz 的时钟速率提供了足够的性能。

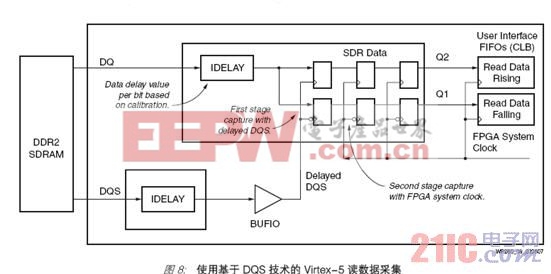

第二种技术称为基于 DQS 的技术。此技术用于更高的时钟速率,Virtex-4 和 Virtex-5FPGA 二者都支持此技术。它使用存储器 DQS 来采集相应的读数据,数据被此 DQS

的延迟信号(通过一个局部 I/O 时钟缓冲器 (BUFIO) 分配)寄存。此数据然后在触发

器的第二级与系统的时钟域同步。IOB 中的输入串行器/ 解串器功能用于读数据采集;第一对触发器把数据从延迟的 DQS 域中传输到系统的时钟域(图8)。

两种技术都涉及到 tap 延迟 (IDELAY) 单元的应用, 在由校验逻辑实现的校验程序中,这些延迟单元会有所变化。在系统初始化期间,会执行此校准程序以设置 DQS、数据和系统时钟之间的最佳相位。这样做的目的是使时序余量最大化。校准会消除任何由过程相关的延迟所导致的不确定性,从而补偿对于任何一块电路板都不变的那些通路延迟成分。这些成分包括 PCB 迹线延迟、封装延迟和过程相关的传播延迟成分(存储器和 FPGA 中都有),以及 FPGA I/O 模块中采集触发器的建立/ 保持时间。有的延迟是由系统初始化阶段的过程、电压和温度所决定的,校准即负责解决这些延迟的变动。

在校准过程中会增加 DQS 和数据的延迟 tap 以执行边沿检测,检测方式是通过连续从存储器中读回数据并对预编写培训模式或存储器 DQS 本身进行采样,直到确定数据选通脉冲 (DQS) 的前沿或前后两沿。之后数据或 DQS 的 tap 数被设定,以提供最大的时序余量。对“基于 DQS”的采集而言,DQS 和数据可以有不同的 tap 延迟值,因为

同步实质上分为两个阶段:一个先在 DQS 域中采集数据,另一个把此数据传输到系统时钟域。

在更高的时钟频率下,“基于 DQS ”的采集方法就变得十分必要,其二阶段方法能提供更好的采集时序余量,因为 DDR 时序的不确定性主要限于 IOB 中触发器的第一级。此外,因为使用 DQS 来寄存数据,与时钟-数据 (Tac) 变化相比较, DQS -数据变化的时序不确定性要小一些。例如,对于 DDR2 而言,这些不确定性就是由器件的tDQSQ 和 tQHS 参数给出的。

正如 Spartan-3 系列 FPGA 中所实现的那样,Virtex-4 和 Virtex-5 FPGA 的写时序由DCM 所支持,此 DCM 生成系统时钟的两相输出。存储器的 DQS 由一个输出 DDR 寄存器来输出,这个 DDR 寄存器由系统时钟的同相时钟驱动。写数据则由超前系统时钟90° 的一个 DCM 时钟输出进行时钟控制。这种技术确保了在 FPGA 的输出部分,DQS 与写操作的数据中心对齐。

此设计的其他方面包括整体控制器状态机的逻辑生成和用户接口。为了使设计人员更容易完成整个设计,Xilinx 开发了存储器接口生成器 (MIG) 工具。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码