一种应用于OFDM系统中的符号精确定时算法的FPGA实

本地相关器的实现是精同步的关键部分,本地相关器的实现中需要用到复数乘法器,本文采用的复数乘法算法如式(5)所示:

由于精同步是与本地序列相关,不存在递推公式,为了降低资源损耗,在选取本地序列时,仅截取实部和虚部的符号位,即每个本地序列的实部和虚部仅用-1,0,1表示,这样每个复数乘法可以转换成加法。

本文对判决函数的计算方法进行了改进,式(3)是对|C(n)|进行一阶泰勒展开,只取0次项与1次项作为|C(n)|的近似结果。

在峰值检测时,本文采用乘法代替除法进行门限判定,门限判决函数如式(6)所示:

|C(n)|>gate*P(n) (6)

达到门限判定条件时,精捕获成功,并通过计数的方式找到FFT窗的位置,完成定时同步。

2.2 FPGA设计方案资源消耗分析

与传统方法相比,本文提出的方案在资源消耗上大大降低,主要体现在以下几个方面:

(1)在本地相关器的实现上。式(5)表明,每次复数乘法运算只需要进行3个乘法运算,节省了1个乘法资源。在进行相关运算时,传统方法在计算每个相关值时需进行384个乘法运算,在本文中,由于实部和虚部都只用符号位表示,乘法器可以用数据选择器与加法器实现,大大节省了乘法器资源。

(2)在判决函数的计算上。传统方法每计算一个判决函数的值,需要进行4个乘法,2个加法计算。本文提出的近似方法中,每次判决函数的计算只需要2次乘法,2次加法,1次比较与1次移位操作,节省了乘法器资源。

(3)在硬件实现时。除法器对资源消耗非常大,本文用比较容易实现的乘法代替传统方法中的除法运算,节省了系统资源。

当然,本文对资源的优化是因为采取了一定的近似处理和截位处理,会带来一定的量化误差,在一定程度上会降低系统的性能,但仿真结果表明,这种性能的损失在可接受范围内。

3 仿真及实现

3.1 仿真结果

利用本地序列截取符号和判决函数的近似对改进方案进行了仿真。该系统中,给定子载波数为N=128,码速率定为Rb=5 Mb/s,子载波间隔为19.2 kHz,数字调制采用QPSK,信道模型选用AWGN模型,设定信噪比为5 dB。

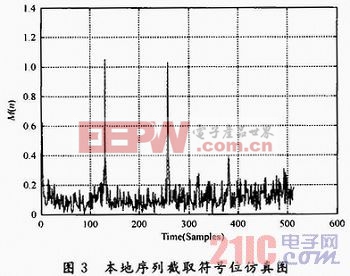

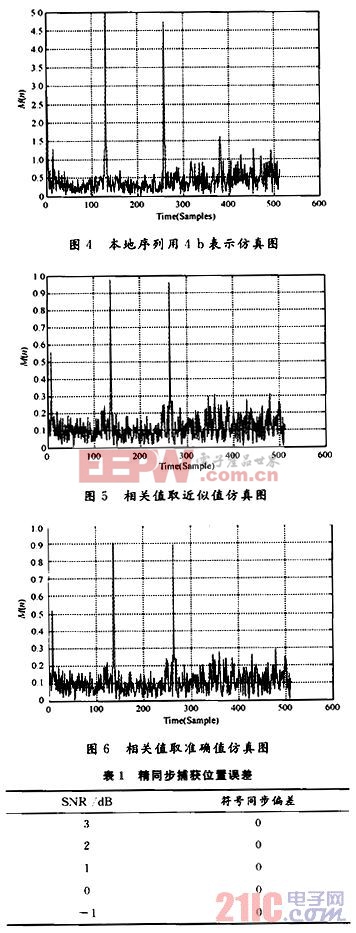

图3是采用本地序列截取2 b的判决函数M(n)的Matlah仿真图;图4是采用本地序列截取4 b的Matlab仿真图。检测峰值时,第一个峰值是由于循环前缀存在的影响,峰值检测时检测第二个峰值。

从图3,图4中可以看出,截位虽然会损耗算法的性能,但是判决函数存在明显峰值,选择适当的阈值时,仍然可以精确定时同步,可见减少本地序列的精度对性能并未造成很大的影响。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码