基于FPGA的高速多路视频数据采集系统

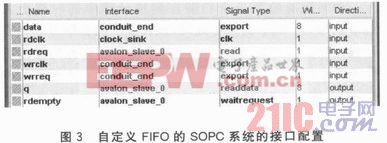

在SOPC自定义器件的配置过程中,根据我们所要实现的功能,FIFO的写入端应为SOPC系统的对外接口,FIFO的读取端应与Avalon总线挂接,并能被DMA控制模块读取。图3为实例化后FIFO模块作为自定义外设引入SOPC系统时的接口配置。

2.4 DMA控制器模块

DMA控制器负责将自定义FIFO接口中的数据搬移至存储区域,每路视频数据源对应一个FIFO接口,每个FIFO接口配有一个DMA通道,各路视频数据的解码、存储互不影响。SOPC系统所支持的DMA控制器IP Core传输模式有3种:

①存储器到存储器模式。这种情况下需要同时打开发送通道和接收通道,而且源地址和目标地址都是自增。

②存储器到外设模式。这种情况下只要打开发送通道,而且源地址自增,目标地址固定。

③外设到存储器模式。这种情况下只要打开接收通道,而且源地址固定,目标地址自增。

本系统设计中,DMA控制器工作任务是将自定义外设存储接口的数据搬移至SDRAM内存中,所以采用第3种DMA控制器工作模式,即从外设到存储器模式。这种工作模式下,源地址是自定义外设的地址,是一个固定地址。而目标地址是SDRAM存储器地址,需要地址自增,在数据传输过程中,由DMA控制器自动完成目标地址自增操作。SOPC系统中的DMA控制器IP Core配置中的DMA寄存器的宽度大小,决定了一次DMA传输所能传输的数据量大小。本设计所需搬移的数据量为一帧图像大小。

2.5 存储空间设计

本系统方案中根据开发板的资源,将多路采集的视频数据分别存储在两块SDRAM中,SOPC系统中两块SDRAM的基地址分别为SDRAM_0_BASE与SDRAM_1_BASE。一块SDRAM中存储的每路视频数据间隔RAM_PROTECT_SPACE的地址空间,DATA_SPACE定义了每路视频数据存储在SDRAM中的预留空间大小。由此可得第n路视频数据在SDRAM中的存储空间的地址。

起始地址:DATA_n_START_Addr=BASE_ADDRESS+RAM_PROTECT_SPACE。

结束地址:DATA_n_END_Addr=DATA_n_START_addr+DATA_SPACE。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码