基于FPGA的可复用通信接口设计

摘要:集成电路设计越来越向系统级的方向发展,解决模块间的接口问题显得尤为重要。 SPI 串行总线是一种常用的标准接口,其使用简单方便而且占用系统资源少,应用相当广泛。 本文将介绍一种新的通用的SPI 总线的FPGA 实现方法。

1、引言

长期以来,外围设备与主机CPU速度之间的不匹配始终困扰着人们,影响了计算机系统更迅速的发展。 随着计算机处理能力及存储规模的迅速增长,这个问题表现得更加突出。虽然已经采取了各种软、硬件的 方法,不断地改善着CPU与I/O设备之间的接口性能。然而,在许多应用中接口问题依然是制约系统性能的 瓶颈。对于特定的设计,设计者面对纷繁芜杂的接口标准,一般根据系统所需的成本及功能选择合适的标 准产品,这可能导致接口标准冲突和引起互用性问题;或许重新选择与接口兼容的标准器件,但又可能会 造成不满足功能需要或成本要求等。

FPGA技术的迅速发展使得接口问题有了好的解决方案。例如,现有的高性能接口IP及高速物理I/O的 FPGA,可满足10Gb/s以上的通信系统的要求;而且用FPGA解决接口不兼容器件间的通信问题。因此本文 将提出一种新的基于FPGA 的SPI 接口设计方法。

SPI(Serial Peripheral Interface)串行外设接口总线[1]是一种同步全双工串行通信接口总线。由于其连线 简单使用方便,故得到广泛应用。在实际开发应用中,若主控制器无SPI接口或需要与多个具有SPI接口的 外设通信,就要使用主控制器的I/O口通过软件来模拟,这就在很大程度上限制了其应用且给数据传输带来 不便。在FPGA技术迅速发展的时代,解决这个问题最方便的办法就是集成一个SPI核到芯片上。

这里根据业界通用的SPI总线的标准,设计一种可复用的高速SPI总线。设计过程中很多变量都采用参 数形式,具体应用于工程实践时根据实际需要更改参数即可,充分体现了可复用性。

2、 SPI 总线原理

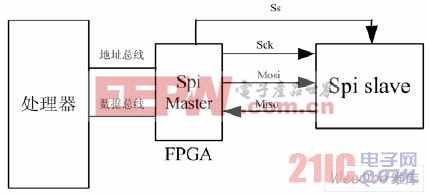

SPI 总线由四根线组成:串行时钟线(SCK),主机输出从机输入线(MOSI),主机输入从机输出线(MISO), 还有一根是从机选择线(SS),它们在与总线相连的各个设备之间传送信息,其连接方式如图1。

图1.SPI总线示意图

SPI 总线中所有的数据传输由串行时钟SCK 来进行同步,每个时钟脉冲传送1 比特数据。SCK 由主机产 生,是从机的一个输入。时钟的相位(CPHA)与极性(CPOL)可以用来控制数据的传输。CPOL=“0”表示SCK 的静止状态为低电平,CPOL =“1”则表示SCK 静止状态为高电平。时钟相位(CPHA)可以用来选择两种 不同的数据传输模式。如果CPHA =“0”,数据在信号SS 声明后的第一个SCK 边沿有效。而当CPHA=“1” 时, 数据在信号SS声明后的第二个SCK 边沿才有效。因此,主机与从机中SPI 设备的时钟相位和极性必须 要一致才能进行通信。

SPI 可工作在主模式或从模式下。在主模式下,每一位数据的发送/接收需要1 次时钟作用;而在从 模式下, 每一位数据都是在接收到时钟信号之后才发送/接收。1个典型的SPI系统包括一个主MCU和1 个或几个从外围器件。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码