采用静态CMOS和单相能量回收电路的乘法器电路设计

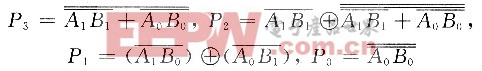

为了能用基本的与非门、或非门和异或门电路实现乘法器,上式可以通过逻辑运算变换为:

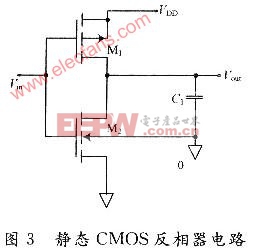

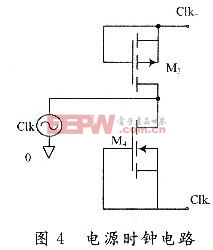

实现电路时,将静态CMOS电路(见图3)构成的与非门、或非门和异或门的电源用图4所示的电源时钟电路代替即可。其中Clk+,Clk-分别接CMOS电路中PMOS和NMOS管的D极和S极。

2.2 仿真结果

在PSpice环境下,分别仿真了用静态CMOS电路和单相能量回收电路构成的两位乘法器电路(见图5和图6),图中只显示了输出4位积的低2位P1P0,其中输入信号A1A0,B1B0波形见图6。其他参数如下:采用CMOS 1.2μm技术,正弦波峰峰值为2.5 V,直流电压VDD为2.5 V,并假设乘法器的输出端接负载电容为O.1 fF。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码