SoC设计之组态性处理器IP介绍

5.针对SoC的应用进行最佳化

SoC的应用非常多,有的是数字相机(DSC)的SoC,有的是可携式媒体播放器(PMP)的SoC,或是导航机(PND)的SoC,不同的SoC其应用设计也不同,例如DSC SoC不重视音讯处理,而PND SoC只专注静态视讯处理及简易的音讯处理,但却需要重视数字信号的处理(接收卫星定位信号后的相关处理),至于PMP、STB(视讯机上盒)则重视动态、高质量的音/视讯处理,也重视信号处理(接收、处理节目信号)。

由上可知,不同的执行处理特性、不同的运算负荷度,若用单一架构处理器IP则难以满足设计,而可组态性处理器IP却可以针对不同的应用需求来进行组态,以合乎各种应用取向的SoC设计。

可组态性处理器IP的隐忧

虽可组态性处理器IP有如上的5种优点,但也不表示没有缺点,事实上,随半导体技术及市场演化,可组态性处理器也面临一些隐忧、威胁,以下我们简要讨论。

1.工艺持续缩密,芯片面积资源获得宽解

芯片的缩密工艺技术仍持续精进,从90nm、65nm、到45nm,并持续往下探,使芯片电路面积成本愈来愈低,因此芯片设计者已不如过往般重视面积成本,事实上处理器的多核化发展,无论是同质多核、异质多核,都表示「透过电路面积倍增的作法来争取效能提升」已属可行、值得。如此,透过组态作法让执行核心的面积最佳化,此种需求将逐渐减少。

2.芯片上市的时间压力愈来愈大

使用IP为的就是要节省芯片设计的验证心力、加速芯片的开发,让芯片更早上市销售,而今市场竞争更加激烈,芯片Time To Market压力比过去更大,使许多SoC项目都舍弃从Soft IP阶段开始设计,直接取用Hard IP加速设计。

然而可组态性处理器IP可说是比Soft IP更Soft(软)性的IP,是从「比Soft IP」更前期的设计阶段开始着手,好处是获得更高的设计弹性,但相对的就是增加SoC的设计时间,甚至为实现组态化而必须学习、熟悉另一套前期设计工具,即处理器的组态工具。

3.软件风险

此点前面已约略提及,事实上,除有软件移植性、兼容互通性等疑虑,软件的后续维护也将令人担忧,同时协力业者提供的宏程序(Macro)也可能无法立即适用,这些都须再行斟酌、调修。特别是软件开发、维护成本在整体SoC方案中所占的比重愈来愈高,许多原有以硬件电路方式设计成的功效,而今多半转成软件方式实现。

4.固定组态处理器IP的转向

ARM、MIPS等皆是以固定组态性处理器IP为主,不过为因应客户需求也开始有些转变,或允许部分的特例,例如MIPS的Pro系列IP就拥有组态性,或如ARM的OptimoDE Data Engines能因应不同需求的应用设计。

附注1:ARM、MIPS在处理器IP的主要授权业务逐渐成熟后,也开始进行相关延伸,如ARM延伸至实体IP领域,MIPS延伸到模拟/混讯IP领域,此外两家业者皆开始跨入32位的控制器IP市场。

附注2:除了Soft IP、Hard IP外也有Firm IP,Firm IP的设计完成度介于前两者之间,不过在产业的实际运用中却不如前两者普遍。

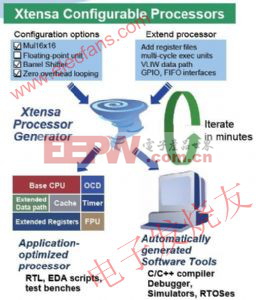

图 Tensilica Xtensa系列可组态性处理器IP的组态设计示意图,左上是勾核需求的功效项、特性项,例如需不需要硬件乘法器、桶式移位器等,右上则是延伸处理器架构,例如增加缓存器、增加VLIW数据路径等,左下则进行必威娱乐平台

最佳化,右下则是软件自动化产生工具。

1

2

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码