DSP的高速串行外设接口设计

3 SPI硬件设计

寄存器在SPI中起着决定性的作用.无论是在微控制器接口,还是SPI控制接口,寄存器在数据传输和控制方面都是主要的组成部分。而寄存器最基本最重要的单元是触发器.只有改善触发器的结构,才能提高整个SPI接口的性能。

有的串行接口设计中采用B结构的触发器设计,这些结构里应用的是一种简单的MOS管做开关.虽然MOS管做开关有功耗低,占面积小的优点。但要提高它的电路工作频率.开关速度,制作丁艺却是越来越困难。而且如果输入信号不强.就很可能出现信号倒流,这就需要一个较高电压来控制开关。这也不利于数据传输和降低功耗等等。

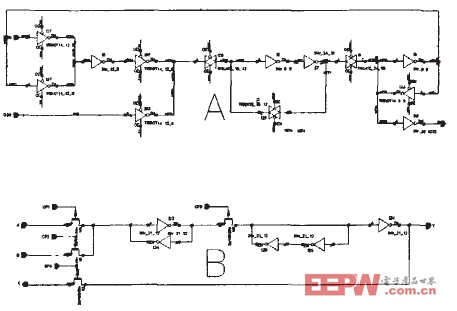

为了解决由MOS管做开关时引起的种种难题.来实现在TMS320LF2407串行接口中的信息传递的高速率。本设计综合考虑速度、工作电压、噪声容限等因素的影响.采用了一种新颖的触发器结构(图4A部分),本文接口电路中大都采用了该触发器的电路设计,工作电压降低到3.3V,大大降低了整体功耗;在开关方面采用了三态门,有效的防止了信号倒流,实现了信号传输的稳定;添加了一个反馈信号,在需要的时候.能够把所需反馈信号再次输入;同时加快r开关速率,带负载的能力也增强。

图4 A、B两种触发器比较

4 RTL级设计

随着数字系统设计的复杂性不断增加,在设计初期指定有效的设计策略对于整个设计是至关重要的。行为描述方式是对系统数学模型的描述。它包括RTL、算法级、系统级的描述。RTL是指通过描述寄存器之间数据流动来描述数字电路系统,是一个数据流的概念.寄存器与寄存器之间的数据处理由组合逻辑完成。RTL级是Verilog较高抽象层次,在这个抽象层次上,模块可以根据设计的算法来实现.而不用考虑具体的实现细节。

4.1寄存器整体电路设计

下面是部分Verilog HDL源代码.描述了数据传输时相关寄存器的功能设置:先是对复位时各个寄存器的初始值,接下来是对寄存器进行功能设计.和数据传输时候产生的中断使能和标志位的设计。

always @ (posedge Peri_clk or posedge RESET)

begin

if(RESET)

begin

outdb=8’hz; SPICCR=8’h00; SPICTL=8’h00; SPIBBR=8’h00; SPIPRI=8’h00;

end

end

always @(posedge Peri_clk or posedge RESET)

begin

if(RESET)

shift_out_d=1’b0;

else

case(1’b1)

spidat_w: SPIDAT=PeriDB; shifi_out_clk:shift_out_d=SPIDAT[7];

sample_in_clk:SPIDAT[7:0]={SPIDAT[6:0],sample in_d};

default;

endcase

end

always@(posedge Peri_clk or posedge RESET)

begin

if(RESET)

SPISTS=8’h00;

else

begin

if(SW_RESET)

SPISTS[7:6]=2’hO;

else if(int_flag_set)

begin

SPISTS[6]=1’b1;SPIBUF=SPIDAT;SPIEMU=SPIDAT;

end

else if(spibuf_r)

SPISTS[6]=1’b0;

if(overrun_flag set)

SPISTS[7]=1’b1;

else if(sts7_clr)

SPISTS[7]=1’b0;

end

end

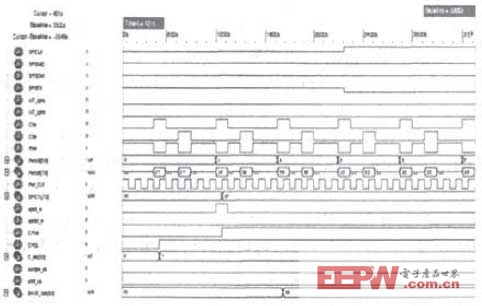

4.2整体时序仿真

将上述Verilog代码编译,再写上对应测试代码进行验证。图5是寄存器的写操作的整体时序仿真波形图.验证了上述代码正确可行。

图5写操作整体时序仿真

5 结论

本文作者的创新点是改进了硬件触发器的结构.用三态门和传输门取代那种单一MOS管的结构。首次应用到TMS320LF2407芯片串行外设接口上,降低工作电压到3.3V,加快数据传输,而且还有相应的反馈信号,进一步完善了触发器结构。同时有很好的可移植性好。具有充分的可裁剪性,本设计运行可靠,达到预期的效果。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码