基于FPGA的高速实时数据采集系统设计

2.2.3 UART模块

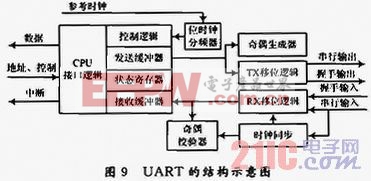

UART即为通用异步收发器,在发送时,将并行数据转换成为串行数据;而在接收端,是将串行数据转换为并行数据。其传送数据主要是以帧的形式进行传输的,一个基本的帧包含有一个起始位、7位或8位数据、奇偶校验位和停止位组成,UART的结构示意图如图9所示。

起始位按照习惯,线路闲置时的逻辑值一般都是1,起始标志的逻辑值为0。对于奇偶校验位的值是所有数据位的异或结果,并且随着数据会一起传输的,如果采用偶校验,当数据中有奇数个1时,那么奇偶校验位就设置为1;如果有偶数个1时,那么奇偶校验位就设置为0。采用奇校验,其结果恰恰相反。对于停止位的逻辑值,一般都是设置为0。

发送模块中引脚功能为:din(7:0):8位并行数据的输入端;sdo:并行数据转串行数据输出端;rst:复位信号输入端,低电平有效;wrn:写控制信号,高电平有效,高电平时写入数据;tsre:并串转换过程标志信号,低电平有效,转换过程中始终保持为0;clk16x:时钟信号输入端波特率发生器产生;tbre:整个工作过程标志信号。

UART模块发送模块在Modelsim中的仿真图如图10所示。

从Modelsim仿真图可以看出,在并串转换过程标志信号(tsre信号)有效时,即为低电平时,则8位并行数据就实现了并串转换,然后通过USB接口传输给上位机显示。

接收模块中引脚功能:rxd:串行数据输入端口;dout[7:0]:并行数据输出端;rdn:写控制端口,高电平有效,此时数据输出;data_ ready:数据是否准备好的标志端口;parity_error:校验位是否出错的标志端口;framing_error:帧是否出错的标志端口。UART模块的接收模块在Modelsim中的仿真图如图11所示。

从Modelsim仿真图可以看出,当UART写控制信号(rdn信号)为高电平,即有效时,则串行数据就实现了并串转换,将上位机的反馈信号传输给系统。

3 结语

本文基于FPGA的高速实时数据采集系统的设计,能够实现数据的高速、实时地采集。系统能够实现6通道同步采集,并通过FIFO解决了A/D转换速率和DSP处理数据的速率不匹配的问题,使系统具有高效、快速的特点。在仿真中验证了所设计功能的正确性,因而在高速实时数据采集方面有着广泛的应用空间。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码