关于Micron和Intel 20nm 64-Gbit MLC NAND闪存的深度探究

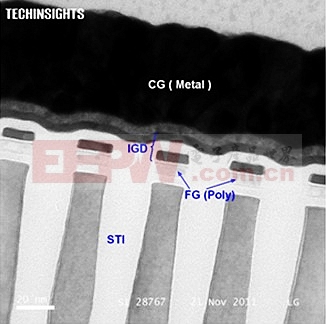

电荷捕捉闪存(CTF)曾被视为另一种选择,因为它拥有平面化的单元结构。不幸的是,我们至今都没有看到它在NAND产品中成功问世。在目前以浮栅为基础的NAND闪存技术条件下,有一种可能的解决方案可用于在20nm节点下进一步缩减NAND闪存的尺寸,即把金属作为控制栅与高K栅极绝缘层(IGD)结合在更薄的浮栅上。

平面浮栅NAND(IMFT20nmNAND闪存)

工艺中的关键技术和新的闪存单元结构

在此类极小的闪存设备上难以使用一些传统的浮栅单元结构。IMFT中具有平面化单元结构的20nm技术,以及先进的工艺技术解决了这一重要难题。

- 将多晶硅控制栅(CG) 填入更窄的邻近浮栅间隙

- 单元与单元间的干扰

- 绝缘膜(IPD)的缩减限度和小型控制栅与浮栅的耦合率

为了制造出20nm NAND单元,在光刻步骤中采用了先进的单元间距缩小技术(例如双重成像技术)。20 nm以下设计规则的图形刻画,也将运用四重成像技术来克服193nmArF沉浸式双重成像技术的局限。但这些可能还远远不够,因为处理这种图形刻画所要求的极紫外光刻(EUV)工具对闪存生产来说太过昂贵。这种NAND元件的单个闪存单元字线和位线方向各自大约40-nm,单元物理面积为0.0017µm2,这种单元可能是所有NAND产品中最小的。该NAND器件采用了平面化浮栅架构,搭配薄型多晶硅浮栅,高介电常数的IGD和金属控制栅。

在这种全新的单元架构中,氧-氮-氧(ONO)的栅间绝缘层被高介电常数的IGD替代,从而还原了在平面单元架构中应当减小的浮栅与控制栅的耦合率。更薄型的多晶硅浮栅技术被用来降低单元间的干扰。金属栅字线是指通过使用硬掩模层来刻画多栅极堆栈结构。单元间距被大幅缩减之后,单元间的耦合电容增加将会是个很严重的问题,因为单元间的干扰增加会降低单元性能,可靠性也成问题。为了解决这些难题,同时在单元栅极之间和第一层金属位线间运用了一种空气绝缘工艺,把气隙架构用作低介电常数的空隙填充材料。位线接触孔的错位布局获得了更好的光刻工艺裕量,并且一个NAND串上有68个字线。

新单元架构结合了IMFT 20nm多层单元闪存中的关键集成技术,具有非常广阔的前景,它可以通过单元尺寸的大幅缩减来进一步延长传统栅极闪存的使用寿命。但是,进一步缩减栅极结构,将会导致电子俘获急剧减少,从而需要在十几nm的多层单元闪存中控制20个以下的电子。正因为这样,一些新颖的器件理论和替代解决方案,例如IMFT的最新NAND闪存器件中所采用的方案,已经做好了在不远的将来替代NAND闪存的准备,这也是由于居主导地位的移动应用对器件尺寸的需求和稳定性的挑战将会更高。近期来看,在NAND产品中见到的结合了3-D构造的电荷捕捉闪存就可以作为替代目前平面化NAND闪存技术的另一种可行选择,与此同时,大量的新型存储理念也开始涌现并且争夺作为NAND闪存替代品的地位。浮栅NAND闪存虽然目前还没有,但最终会达到它的尺寸极限。在不远的将来,看看IMFT以及其他闪存制造企业将如何变革去克服这些尺寸极限,将会非常有趣。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码