采用边界扫描法测试系统级芯片互连的信号完整性

监视BSC(OBSC)

建议在互连的接收侧放置一个新的使用ILS单元的BSC,如图5所示,这种新的BSC被称为监视BSC (OBSC)。ILS被加在接收侧单元,它们能够捕获互连末端上带噪声和时延的信号。如果它接收到具有完整性问题(如时延破坏)的信号,它会在输出端输出 一个脉冲,并将触发器置为“1”。OBSC有2种工作模式:

1) 完整性模式(SI=1):选择信号F。在每个Shift-DR状态通过扫描链输出被捕获的完整性数据,并用于最终的评估。

2) 正常模式(SI=0):在这种模式中ILS被隔离,每个OBSC被当作标准BSC使用。

在扫描输出过程中,我们需要捕获输出F信号并送至FF1。在本例中sel应置为0,因此SI和ShiftDR应分别为1和 0。当扫描输出过程开始后,D1被传送到Q1,并用作下一个单元的TDI。信号完整性信息被捕获进FF1后ILS触发器复位。在将F值送至Q1后,必须格 式化扫描链。在本例的Shift-DR状态期间,TDI输入必须连接至FF1。因此必须将sel置为1(SI=’1’,ShiftDR=’1’)从而隔离 出ILS路径。如图5所示,SI和ShiftDR需要进行或操作,以选择和发送信号F到D1,并生成扫描输出用的扫描链。

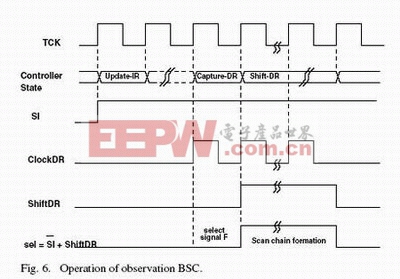

图6显示了sel与SI和ShiftDR间的从属关系。如图所示,在Capture-DR状态,信号F被选中,扫描链在 Shift-DR状态得到格式化,并根据被测试的线数扫描输出数据。表1给出了信号sel的真值表。只有一个控制信号(即SI)是由新指令生成的。执行信 号完整性信息的监视有三种方法:1)应用每个测试模式后读出;2)应用测试模式子集后读出;3)应用整个测试模式后一次性读出。具体选择哪种方法取决于可 接受的时间开销。第1种方法非常耗时,但它可以尽可能详细地显示每个互连的完整性信息。第3种方法速度非常快,但完整性信息比较少,因为只能得到哪个模式 或哪个模式子集引起完整性故障的信息,无法获知故障类型。方法2可以帮助用户在测试时间和准确性之间取得平衡。

测试架构

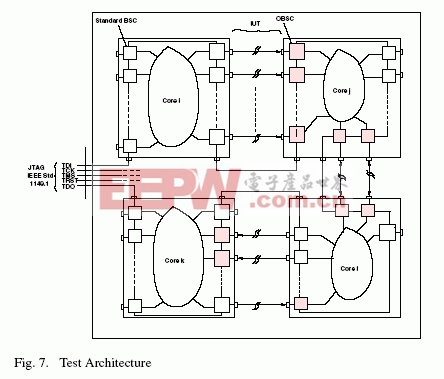

图7给出了针对小型SoC的整体测试架构,其中的JTAG输入(TDI、TCK、TMS、TRST和TDO)使用时没加任何 修改。但定义了一条新的指令,主要用于信号完整性测试中读取测试结果。从图7可以看到,只是每个互连的接收端单元改成了OBSC。对于双向互连,OBSC 单元用于Core j和Core1之间的双侧。其它单元都是标准BSC,在信号完整性测试模式期间出现在扫描链中。ILS的作用是独立的,不需要特殊的控制电路来控制这类单 元的时序。由F显示的完整性信息被扫描输出,用以确定有问题的互连。

1. EX-SITEST指令

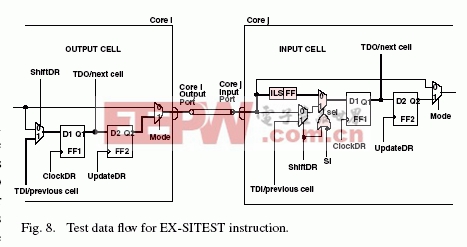

针对新的测试架构,建议在IEEE 1149.1指令集中增加一条新的指令EX-SITEST。这条指令类似于EXTEST指令,但增加了控制信号SI。在Update-IR状态,这条指令 被解码并产生(SI_1)。此时输出单元用作标准BSC,而输入单元用作OBSC。信号F在Capture-DR状态时被捕获,并在Shift-DR状态 期间以每个时钟周期的速度向外移位输出。本例中TAP控制器状态不会改变,但在指令解码时需要一些变化。存在于内核之间的EX-SITEST指令的数据流如图8所示。

2. 测试过程

首先通过EX-SITEST指令装载TAP控制器IR,然后将所有的测试模式应用到互连上,同时ILS单元捕获互连末端的信 号,并检测所有可能的故障。在测试应用过程结束后,必须读取存储于ILS单元FF的结果。监视过程可以利用3种方法之一。比如使用方法3,应用所有测试模 式,然后一次性读出完整性信息。

3. 测试数据压缩

在传统的边界扫描架构(BSA)中,测试模式是一个一个扫描进来并应用到互连上。举例来说,采用最大入侵方(MA)故障模型 的n位互连中,12个测试模式被应用到每个受害线,在将测试模式应用到受害线上时要求12n 时钟。在n个互连间翻转受害线,总的时钟数量(测试应用次数)是12n2。当然,MA是一个简化模型。如果采用更复杂的模型或SoC中具有大量互连时,测 试模式数量会激增,此时压缩就显得很有必要了。本文介绍一种针对增加边界扫描架构的简单有效的压缩技术。由于空间有限,本文只能作一简要介绍,以此说明增 加型JTAG架构的灵活性。

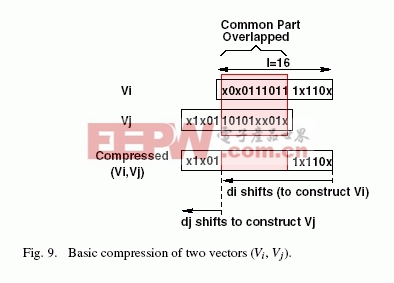

这种压缩技术有二个关键点。首先,我们的方法是一个简捷的无损压缩法,通过确定相邻二个模式间的最大相似性并覆盖它们来构筑压缩位流。其次,由于这种压缩法即无破坏性也不对模式重新排序,因此不需要额外的解压缩硬件。而且仅是利用自动测试设备(ATE)通过控制JTAG TMS控制输入端执行解压缩过程。当测试模式产生后,常会有大量无关紧要的模式出现在测试模式集中。针对信号完整性产生的模式也是这样,特别是在考虑了地 区度量标准时(限制开发模式空间)更是如此。在任何情况下我们都假设测试集由相同长度的包含不重要的模式组成。图9表达了我们的基本压缩想法,即充分利用 不重要的部分覆盖尽可能多的位来完成2个模式Vi和Vj(长度是1_16)的压缩。

本文小结

在本例中,压缩后的数据(Vi,Vj)扫描输入时只需要21个时钟,而未压缩的数据需要16+16=32个时钟。需要注意的 是,为了解压缩指定的数据流,我们需要一个模式一个数字(如本例中的di和dj)才能构造(解压缩)模式。基于边界扫描测试的目的,这些数量就是更新 BSC单元内容前要求的移位(即时钟)数量。我们假设ATE存储着解压缩数据(d值如0≤d≤1),在扫描输入位流时,该数据会在d个时钟后激活TMS (测试模式选择)信号。然后TMS信号促使TAP控制器产生用于信号完整性测试的正确控制指令(如EX-SITEST)。因此在我们的架构中不需要额外的 解压缩硬件。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码