基于DSP+FPGA的高精度程控交流电源设计

3.2 逆变电路设计

逆变电路采用SPWM方式。由于调制后的信号中除含有调制信号和高频率的载波频率及载波倍频附近的频率分量外,几乎不含其他谐波。因此,提高开关频率可消除逆变器的低次谐波,减小谐波损耗,但开关频率过高会使逆变器的开关损耗及电磁干扰大幅增加,同时给DSP的运算及D/A转换带来压力。此外,死区时间在脉宽中所占的比例过大也会造成占空比丢失。因此,从开关器件的损耗、谐波失真度之间折中,选取开关频率为80 kHz。由于单极性调制产生的波形失真较大,这里采用双极性调制技术。全桥的4个功率管都工作在较高的载波频率,同一桥臂的两个功率管互补导通,可得到较为理想的输出波形。

为降低调制复杂程度,采用异步方式SPWM技术实现频率输出的精密控制,保持调制频率(即开关频率)fc固定不变,通过改变载波比N完成fo的变化。由于电源最高输出频率只有1 kHz,所以N较大,一周期内脉冲数较多,脉冲不对称产生的不利影响较小。

设计中采用电压跟踪控制方法生成SPWM波形,可实现高精度输出。该方法具有高频滤波设计简单,输出谐波小的优点,其产生的误差在工程上可忽略不计。工作原理如下:采用闭环控制,将希望输出的波形作为指令信号U*,将实际波形作为反馈信号U,通过两者的瞬时值比较来决定逆变电路各器件的通断,使实际的输出跟踪指令信号变化。在比较控制过程中,设置一个固定的时钟,以固定采样周期对指令信号和被控量采样,按偏差的极性来控制开关器件通断。在时钟信号到来时刻,若UU*,令功率开关导通,使U增大;若U>U*,则令功率开关关断,使U减小。这样,各采样时刻的控制作用都使实际电压与指令电压的误差减小,只要N足够大,即可保证电压跟踪控制精度。考虑到功率器件的开通和关断都需要时间,为防止上下臂直通造成短路,需设置一定的死区时间。因此,实际电路工作时,考虑到功率器件的开通和关断时间,调制度M=0.85。最大输出电压有效值为300 V,故前级电压输出应为:![]() /0.85=500V。逆变电路关键参数设计过程如下:

/0.85=500V。逆变电路关键参数设计过程如下:

(1)输出滤波器的设计

①滤波电感:最大纹波电流取满功率输出正弦电流峰值的30%,即![]() 。而纹波电流△i=[(ui-Uo)/L](D/fs)=(ui-uo)uo/(Lui),其中ui为前级输出电压,D为占空比。由上式可知,当uo=0.5ui时,△i最大,故有:△Imax=ui/(4Lfs),所以L=1.49 mH,取1.5 mH。

。而纹波电流△i=[(ui-Uo)/L](D/fs)=(ui-uo)uo/(Lui),其中ui为前级输出电压,D为占空比。由上式可知,当uo=0.5ui时,△i最大,故有:△Imax=ui/(4Lfs),所以L=1.49 mH,取1.5 mH。

②滤波电容:滤波电感、电容一起构成低通滤波器。SPWM方式下,为滤除高次谐波成分,取滤波器截至频率为开关频率的1/10,即![]() (2πfs)/10,故C=0.26μF。为消除器件非理想特性及死区等影响,电容值需大一些,设计中取为1μF。

(2πfs)/10,故C=0.26μF。为消除器件非理想特性及死区等影响,电容值需大一些,设计中取为1μF。

(2)陷波器的设计

为进一步降低谐波失真,在输出滤波器后侧设置了两级陷波器电路,电路如图3所示。

图中,L1与C1构成第一级陷波器,用于滤除开关频率噪声,谐振频率取fs(80 kHz),取C1=2μF,则L1=[1/(2πfs)2]/C1=2μH;L2与C2构成第二级陷波器,滤除开关频率二倍频噪声。谐振频率取为160 kHz,取C2=2μF,则L2=500 nH。

4 实验结果

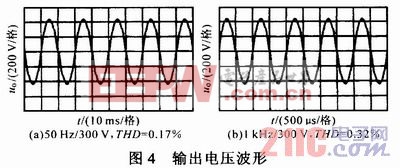

在样机上进行了实验验证。额定输出功率750 VA,可实现频率变化范围45 Hz~1 kHz,频率分辨率为10 μHz,电压变化范围0~300 V。满载300 V正弦电压输出波形uo如图4所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码