扩频通信系统CCSK信息调制解调算法设计

2.2 多路并行CCSK数字相关器算法设计

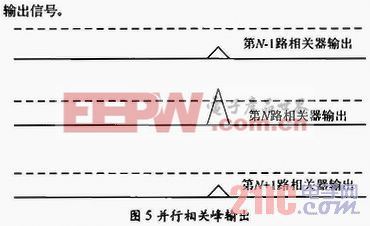

多路并行型CCSK数字相关器输入的的是m序列N次循环移位码,如32 bit系统中,m序列N次循环移位码有32种,接收方可以通过32个32 bit并行数字相关器对基带码流进行相关处理。当输入码流同第N路相关器的相关输出超出信号门限时,则认定接收到的数据为N,图5所示就是并行相关峰输出信号。

多路并行型CCSK数字相关器的电路结构比较简单,对电路时序的要求也较低,相关器输出时序位置固定,不需要进行时间差计算提取信息,也不需要对部分相关峰进行时序处理,故可采用对加法进位延迟要求较低的流水线加法器型数字相关器作为相关处理的核心部件。但是,多路并行型CCSK数字相关器消耗的硬件资源在同样码速率和码长时,比两级串联型CCSK数字相关器要多若干倍,因此,32 bit扩频系统中采用多路并行型CCSK数字相关器要比两级串联型CCSK数字相关器所消耗的资源多16倍。

3 结语

本文对CCSK信息的调制和解调算法进行了介绍,给出了CCSK逻辑编码电路的实时计算方法,同时对两级串联型CCSK数字相关器算法和多路并行CCSK数字相关器算法的设计进行了说明。采用直序扩频的通信系统具有较高的抗干扰能力,但通信信息速率会大幅下降。因此,在通信速率和抗干扰之间找到一个平衡点,是扩频通信系统的一个重要技术问题。而利用本文提出的CCSK编码解码技术可以有效地提高扩频通信系统的通信速率。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码