基于DSPBuilder的FIR滤波器的系统设计

4.3 基于DSPBuilder的滤波器仿真

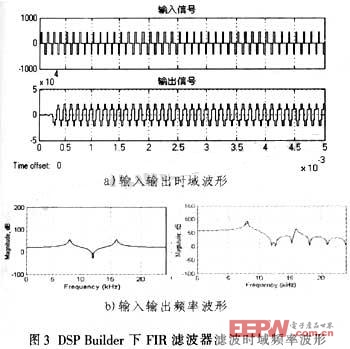

输入信号分别采用频率f1=8KHz和f2=16KHz的两个正弦信号进行叠加。其中的仿真波形如图3所示,从FIR滤波电路的仿真结果看出,输入信号通过滤波器后输出基本上变成单频率的正弦信号,进一步通过频谱仪可看出f2得到了较大的抑制,与条件规定的fc=10.8kHz低通滤波器相符合,至此完成了模型仿真。

4.4 运用Modelsim进行功能仿真

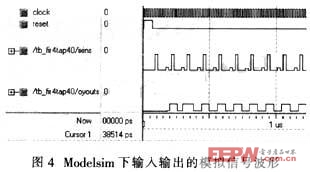

在Simulink中进行的仿真是属于系统验证性质的,是对MDL文件进行的仿真,并没有对生成的VHDL代码进行过仿真。事实上,生成VHDL描述是RTL级的,是针对具体的硬件结构的,而在Matlab的Simulink中的模型仿真是算法级(系统级)的,是针对算法实现的,这二者之间有可能存在软件理解上的差异,转换后的VHDL代码实现可能与MDL模型描述的情况不完全相符,这就是需要针对生成的RTL级VHDL代码进行功能仿真。

在此,笔者利用Modelsim对生成的VHDL代码进行功能仿真。设置输入输出信号均为模拟形式,出现如图4所示的仿真波形,可以看到这与Simulink里的仿真结果基本一致,即可在QuartusⅡ环境下进行硬件设计。

4.5 在FPGA器件中实现FIR滤波器

在QuartusⅡ环境中打开DSPBuilder建立的QuartusⅡ项目文件firl.qpf。在QuartusⅡ中进行再一次仿真,由此可以看到符合要求时序波形,然后指定器件引脚并进行编译,最后下载到FPGA器件中,就可以对硬件进行测试,加上CLCOK信号和使能信号,用信号发生器产生所要求的两个不同频率的正弦信号,就可以在示波器上看到滤波以后的结果,需要设计不同的滤波器电路时,仅修改FIR滤波模型文件就可以实现,这样不仅避免了繁琐的VHDL语言编程,而且便于进行调整。

5 结束语

在利用FPGA进行数字滤波器的开发时,采用DSPBuilder作为设计工具能加快进度。当然,在实际应用中,受精度、速度和器件选择方面的影响,可以对其转化的VHDL进行进一步的优化。

关键词: DSPBuilder FIR滤波器 FPGA Simulink

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码