基于VHDL的感应加热电源数字移相触发器设计方案

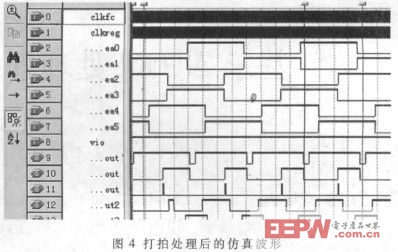

由于同为两相电压产生的两路同步信号,频率、幅度相同,相位差半个周期。为了节省芯片资源,可将同两相电压产生的两路同步信号进行异或处理,异或处理之前要对两路同步信号进行“打拍”处理,两路同步信号“打拍“的次数决定着负脉冲的宽度,仿真波形如图4所示。plusea0与plusea1打拍后,作异或运算及仿真结果。

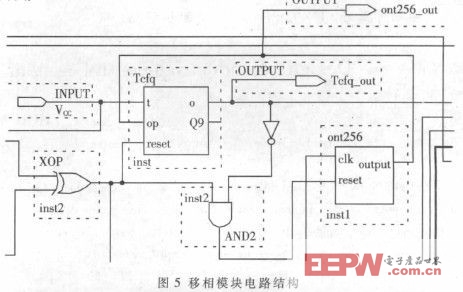

移相模块电路结构如图5所示。移相触发模块由T触发器、两个逻辑门和计数器组成。当计数器输入由‘0’变成‘1’时,计数器开始计数。当计数溢出时,送出窄脉冲进位信号导致T触发器输出高电平,从而实现对计数器的复位,等待下一个脉冲到来时重新计数,实现了循环计数自动清零功能。

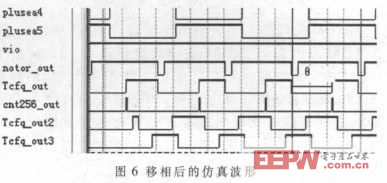

经过移相仿真后波形如图6所示。相位移动角度为θ,相位移动的参考基准是异或门的负脉冲,即得到的触发时刻是相对于同步信号延迟θ角后的时刻。

三相电的一个周期包含6个换相区,若晶闸管脉冲触发模块采用单脉冲触发,经实验发现,当电网电压波动时,会出现漏触发现象。

2.2改进策略

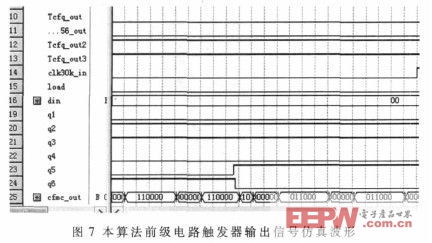

本算法中脉冲触发模块的设计由触发相区判断单元和触发脉冲单元两部分构成。判断单元的作用是根据前级电路触发器输出的6路提示信号(如图7中q1~q6),判断当前移相角所应对应的换相区间。脉冲触发单元是根据判断单元结果决定所需要触发的晶闸管对。 本算法中采取锁相环倍频措施,将脉冲触发模块的同步时钟在系统时钟基础之上进行倍频处理,本系统中主时钟为20MHz,脉冲触发模块同步时钟倍频至100MHz,算法中采用多脉冲连续触发的方式,即换相触发时刻到来时,由触发脉冲单元在高频时钟的同步下,连续触发相应的晶闸管,确保不出现漏触发现象。仿真波形如图7所示。

触发脉冲单元根据判断单元送出的6路当前触发提示信号,对应相应的晶闸管进行连续触发。脉冲触发单元输出的六位信号经过脉冲变压器分别对应触发图1所示晶闸管的标号。

3实验结果

从仿真结果看:触发脉冲稳定连续,能够满足使用要求。采用双通示波器能够清晰地看到对应的两个触发脉冲(实验中采用的示波器是AgilentDSO3062A)。通过仿真和相应波形测试证明:该数字触发器简单可靠,产生的脉冲稳定、连续、抗干扰能力强。本系统正应用于200kW大功率感应加热电源的三相全控整流桥。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码