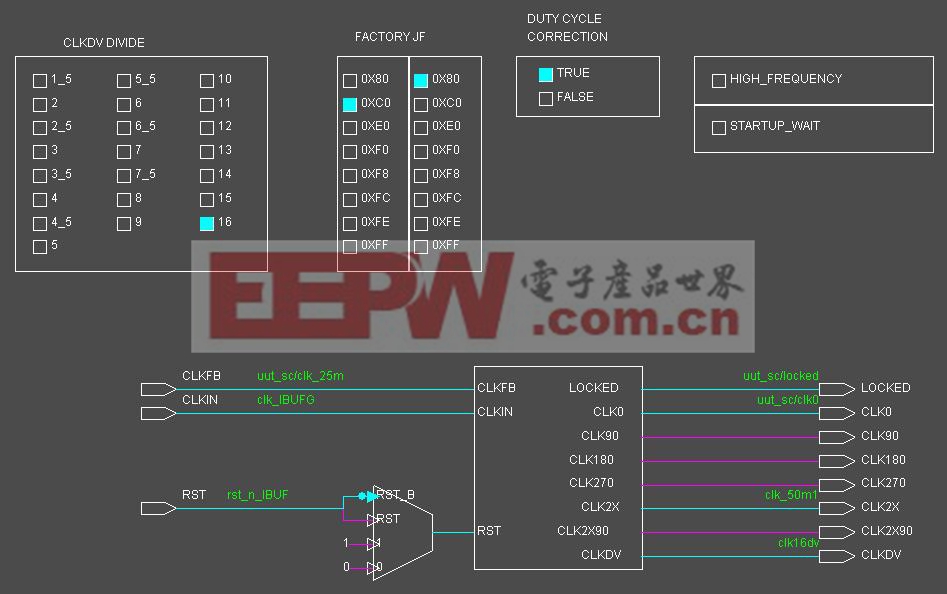

DCM和DLL使用带来的思考

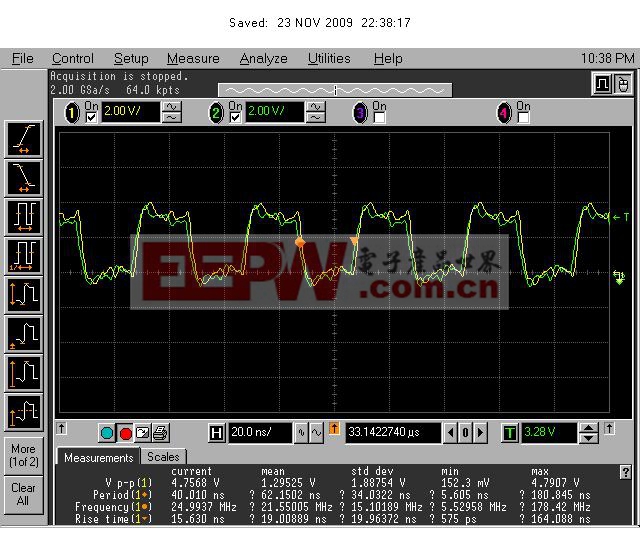

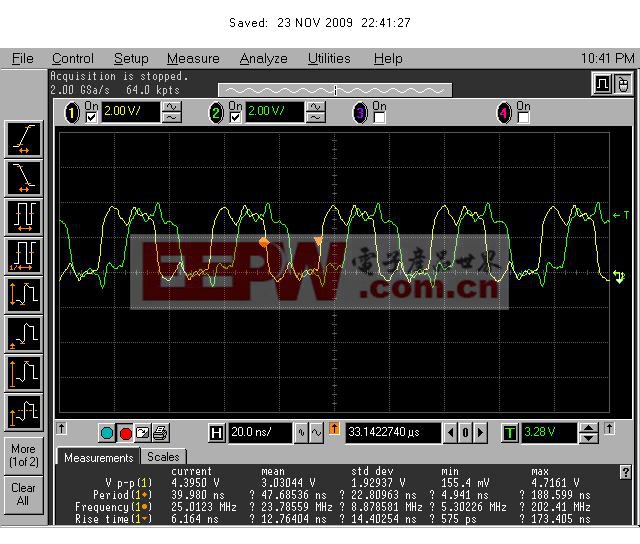

图2黄色:clk00 绿色:clk0(BUFG前)

图3

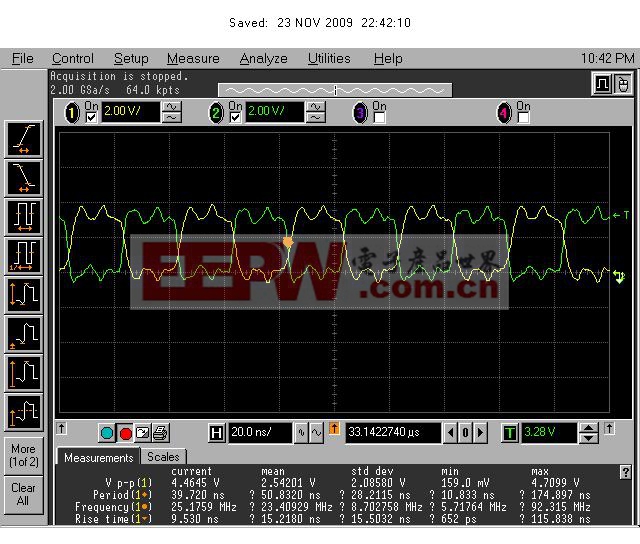

黄色:clk00 绿色:clk2x(2倍频时钟)

图4

黄色:clk00 绿色:clk90(90度相移)

图5

黄色:clk00 绿色:clk180(180度相移)

图6

图7

对于时钟偏斜的改善也是显而易见的,原先的clock path skew/delay(也即clock network latency)一般在1到2ns,现在都在-0.5ns到0ns。至于为什么这个skew值可以是负值呢?特权同学看了很多资料,都只是轻描淡写的说DLL是通过外部的反馈时钟,然后调节内部的延时实现最终的skew的减小。从clock skew的定义来看,时钟从输入到各个寄存器的延时不可能是负数的,惟一的可能是经过DLL后的时钟被整个的延时了大约1个时钟周期,从而达到下一个时钟沿和上一个时钟沿对齐的效果,那么这个clock skew为负值就不难解释了。

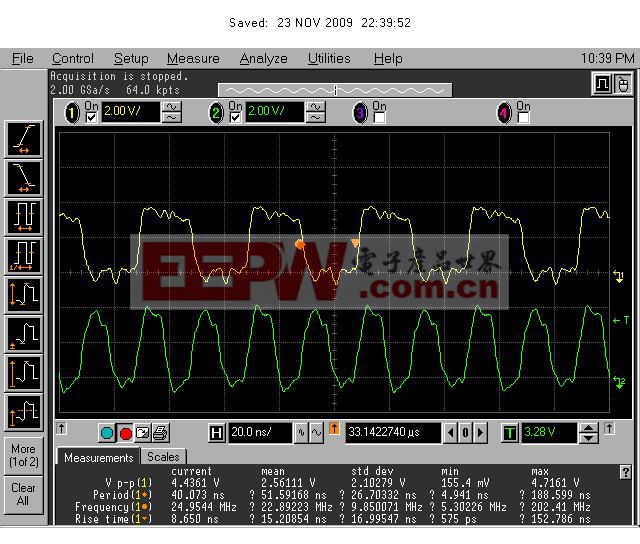

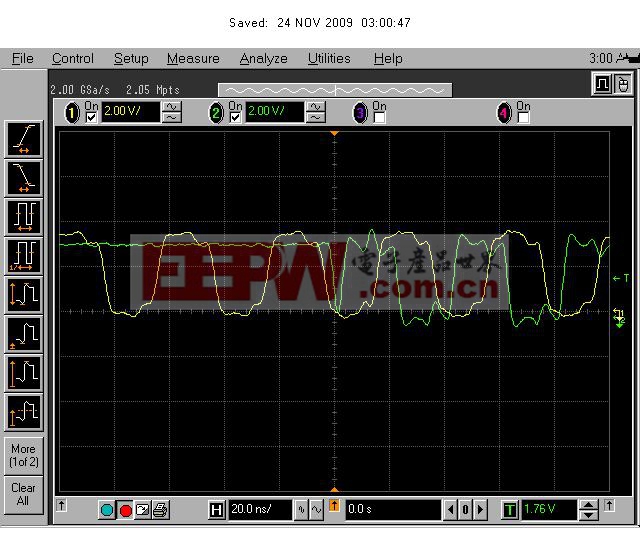

特权同学也特意从上电开始捕获了DLL输出时钟(引到了输出PAD上,这个延时也不小),和时钟的输入(FPGA的输入PAD)做了对比。发现确确实实有那么一个相位的调整过程。而且这个相位的调整是在DLL输出开始时,输出时钟滞后输入时钟将近270度,如图9所示;图10捕获到了更为明显的相位调整,即从中线左侧到右侧的变化。正常稳定后的输出如图11和图12所示,相位依然滞后而不是负值那是因为我所捕获的这个输出时钟是拉到了PAD上的缘故,延时大了一些也在所难免。绿色为输入时钟,黄色为DLL输出时钟引到PAD上。

图8 上电的整体信号捕获

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码