基于FPGA和ARM的彩色图像处理系统

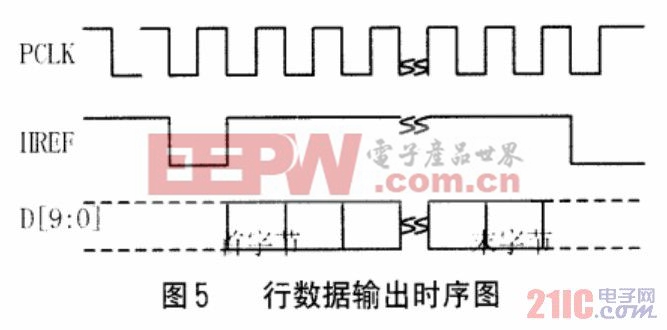

系统配置完毕后,便可进行图像数据的采集。图4和图5是数据采集与输出的时序图。其中VSYNC是场同步信号。HREF是水平同步信号。 PCLK是象素数据输出同步信号。HREF为高时即可开始有效数据采集,而PCLK下降沿的到来则表明数据的产生,PCLK每出现一个下降沿,系统便传输一位数据。在HREF为高电平期间,系统共可传输640位数据。在一帧图像中,即VSYNC为低电平期间,HREF会出现480次高电平。而下一个 VSYNC信号上升沿的到来则表明分辨率640×480的图像采集过程的结束。

3.2 FPGA与ARM的数据交换

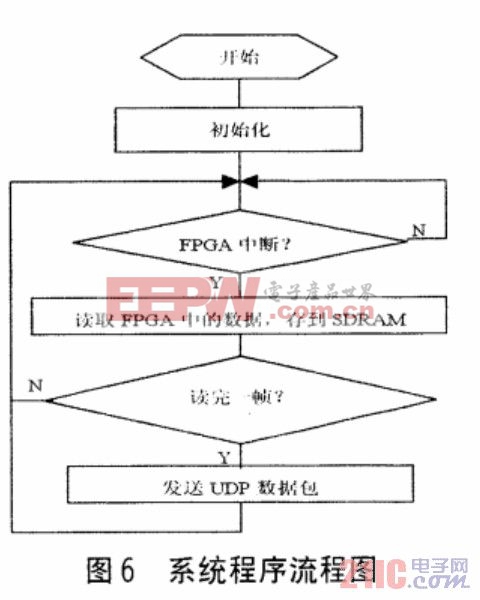

FPGA内部用一个8 KByte双口SRAM作为图像存储区。为了实现图像数据的实时采集与处理,应使图像数据的采集与外部图像数据的读取同时进行。因此本系统采用双缓存结构。实现方法是把8 KB的SRAM划分成两个大小为4 KB的SRAM(设为SRAM1和SRAM2),每片SRAM一次存储六行图像数据。这样,在同一时刻,一片可用于存储图像数据,另一片可用于外部ARM 对图像数据的读取。两块SRAM存储区乒乓式切换。当图像数据写满SRAM1时,FPGA向ARM发送一个中断信号,之后,ARM响应中断并读取 SRAM1中的图像数据,同时将其写入到SDRAM中。之后,图像传感器的数据将写入SRAM2,当图像数据写满SRAM2时,FPGA也向ARM发送一个中断信号。ARM响应中断并读取SRAM2中的图像数据.同时将其写人到SDRAM中。之后,图像传感器的数据将再次写入SRAM1。

3.3 以太网数据传输的实现

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码