基于C64x+ DSP高速缓存一致性分析与维护

硬件维护的CACHE一致性

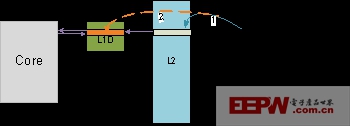

在C64x+平台上,硬件会对5)的情况自动进行数据一致性维护。分析需要分为读写两类操作进行,图 5和图 6分别描述了内核对L2上的数据进行读和写的情况。

图 5 内核读L2数据的情况

图 6 内核写L2数据的情况

其它主机要对L2中的内容进行更新操作时,L2控制器会根据被更新数据的地址判断相应的地址是否在L1D CACHE中,如果在L1D CACHE中,硬件会自动将更新的数据拷贝一份到L1D CACHE中。如果要读取的数据不在L1D CACHE中,L1D控制器会自动从L2加载数据,内核也可以得到更新后的数据。过程如图 5中的1和2所示,这样就可以解决一致性的问题。

其它主机要对L2中的内容进行读操作的时候,L2控制器会判断要读取的数据地址是否在L1D CACHE中,对于在L1D CACHE中的数据,硬件会自动从L1D CACHE中读取最新的数据。对于不在L1D CACHE中的数据,说明L2中的数据已经是最新的数据,可以直接从L2中读取。通过这样的处理,可以保证其它主机读到内核更新后的数据,从而可以解决一致性的问题。过程如图 6中的1和2所示。

软件维护的CACHE一致性

在C64x+平台上,2)、3) 和6)的情况需要软件进行的一致性维护操作以保证内核或者其它主机可以得到最新的数据。

C64x+ 软件一致性维护实现

C64x+平台上由软件控制的一致性维护操作包含三种:CACHE数据失效、CACHE数据回写和CACHE数据回写并失效。启动维护操作需要配置相应的基地址和计数寄存器,当计数寄存器中的值变为0时表示操作完成。TI提供的芯片支持库中也提供了相应的API来完成相应的功能。各种操作涉及的各级CACHE的一致性操作控制寄存器列在表2中。

表 2 C64x+ CACHE一致性维护寄存器

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码