串行RapidIO: 高性能嵌入式互连技术

串行RapidIO基于现在已广泛用于背板互连的SerDes技术,它采用差分交流耦合信号。差分交流耦合信号具有抗干扰强、速率高、传输距离较远等优点。差分交流耦合信号的质量不是由传统的时序参数来衡量,而是通过眼图来衡量,眼图中的“眼睛”张得越开则信号质量越好。图5是一个典型的串行RapidIO信号眼图。

图5 串行RapidIO信号眼图

为了支持全双工传输,串行RapidIO收发信号是独立的,所以每一个串行RapidIO口由4根信号线组成。标准的1x/4x 串行RapidIO接口支持4个口,共16根信号线。这4个口可被用作独立的接口传输不同的数据;也可合并在一起当作一个接口使用,以提高单一接口的吞吐量。TI的TMS320C6455 DSP上集成了标准的1x/4x串行RapidIO接口,如图6所示。

图6 TMS320C6455集成了1x/4xSRIO接口

发送时,逻辑层和传输层将组好的包经过CRC编码后被送到物理层的FIFO中,“8b/10b编码”模块将每8位数据编码成10位数据,“并/串转换”模块将10位并行数据转换成串行位,发送模块把数字位转换成差分交流耦合信号在信号线上发送出去。接收的过程则正好相反。

串行RapidIO在无线基础设施上的应用

无线基础设施如基站、媒体网关等,是典型的高性能嵌入式通信系统,它们对互连的带宽、时延、复杂度、灵活性和可靠性都有非常高的要求。而串行RapidIO正是满足这些要求的最佳选择。

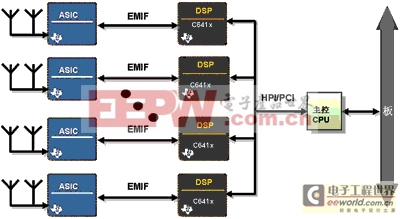

以无线基站为例,在SRIO出现之前,无线基站的基带处理的典型框图如图7所示。

图7 传统无线基站基带处理框图

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码