基于FPGA的HDB3码编码器优化设计与分析

2.2 HDB3极性变换

在极性变换中,将使用四选一模拟开关实现+1,0,-1的波形输出。实现真正意义的HDB3码的输出,这里选用的是数字芯片CD4052来实现。

在单双极性变换设计与实现部分,要实现将3位的编码转换为2位的编码,也就是将前面的+1,-1,+V,-V,+B,-B,0转换成用两位来标识,这样才能通过CD4052的两个输入端进行不同的组合,从而选通不同的通道,实现HDB3码的+1,-1,0三种电平的输出。而转换的方法和编码时确定的极性是一致的,分别用10,01,00来标识+1,-1,0。在数字示波器下观测到的波形如图3所示。

2.3 结构化HDB3码编码器设计

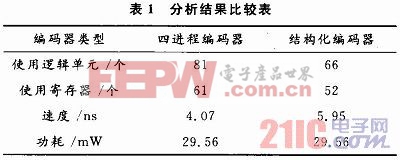

在该设计中,将使用元件例化语句来实现HDB3码编码器。底层文件主要分为序列发生器、插“V”模块、插“B”模块、单双极性变换模块,加上顶层文件共5个模块。在该设计中,用11标识+1,01标识-1,用00标识0。其中codeinout是用来观察序列发生器产生的二进制代码序列,做为HDB3码编码器的输入序列,codeout为HDB3码的编码输出。该设计运用VHDL硬件描述语言的元件例化语句来实现HDB3码编码器的设计,共一个顶层文件和4个底层文件。在编码中,选用2位二进制对HDB3码编码的插“V”和插“B”以及输出进行编码,且用的均为非归零码来表示。对元件例化语句二位编码的设计进行波形仿真结果如图4所示。

从图4中可见,输出的编码序列和编码规则一致,说明设计正确。

3 HDB3码编码在FPGA中实现的特性分析

选用cycloneⅡ系列EP2C5T144C6器件,利用QuartusⅡ7.2对两种不同设计的HDB3编码器进行了分析。分析的主要内容包括:逻辑单元的占用、寄存器的占用、工作速度及功耗等的比较。仿真之后,主要选择了两组结果进行比较。分析结果如表1所示。从仿真结果可以看出,在结构化设计中,编码器总逻辑元件、专用寄存器使用与四进程设计相比各减少了18.5%,14.8%,表明结构化设计有利于减少器件资源的使用。

4 结语

根据实验和系统分析的结果,在FPGA中,利用VHDL语言设计HDB3编码器是可行的。尤其是结合VHDL语言程序设计的特点,利用不同的设计方式,可实现对HDB3编码器的优化设计。通过比较,在结构化设计中,编码器总逻辑元件、专用寄存器使用与四进程设计相比各减少了18.5%,14.8%。因此,结构化设计有利于减少器件资源的使用。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码