短波段频率合成器的设计与调试

2.3 环路滤波器

环路滤波器的Multisim幅频特性仿真结果如图7所示。分析得知,在-3 dB处频宽1 kHz,满足设计要求,带内波动相对平坦,环路低通特性比较陡峭,锁相环稳定性得到提高。

3 性能测试与分析

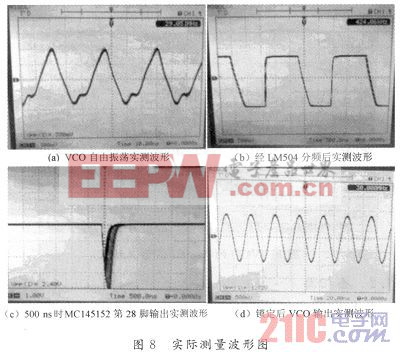

如果实验室没有配置频谱仪等高档仪表,使用数字存储示波器也能比较准确地测试锁相环频率合成器的性能,实际测量结果如图8所示。分析如下:

(1)图8(a)测试结果显示,VCO自由振荡时频率在29 MHz左右,波形失真较大;

(2)图8(b)测试结果显示,前置ECL分频器64分频后输出方波,下降延迟较大,这是ECL内部结电容所致,而后级分频采用上升沿有效,因而对系统性能无影响;

(3)图8(c)测试结果显示,MC145152第28脚输出信号,向下的窄脉冲小于50 ns,说明瞬态相位偏差小,说明锁相环比较稳定;而上升沿的抖动即为相位噪声的反应,抖动范围小于20 ns,说明相位噪声比较理想;

(4)图8(d)测试结果显示,环路锁定后,测量VCO输出信号,频率达到30 MHz,幅度到达1.7 Vpp,波形良好,无失真。

4 结语

锁相环路是一种以消除频率误差为目的的相位误差反馈控制电路。随着现代电子技术的发展,具有高稳定性和准确度的频率源锁相环已经成为通信、雷达、仪器仪表、高速计算机及导航系统的不可或缺的关键部件。本系统基于锁相环实现短波段正弦信号的生成,实现了无频差的频率跟踪和相位跟踪,并用基本仪表测试了其性能,测试结果良好。本文从基本理论和工程实践的层面,分别介绍了上述频率合成器的设计流程和调试方法,对从事无线电设备工程设计和生产调试的技术人员,尤其对高等院校教学实验室的实验员掌握使用简陋仪表测试锁相环频率合成器的性能,具有一定的参考价值。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码