用CPLD创建具有弹性指令集的微控制器

从消费类产品到通信产品,微处理器都有着非常广泛的应用。目前流行的8位微处理器不仅能够完成高运算量的任务,而且成本很低,因此取得了巨大成功。微处理器非常擅长于有序处理和各种非实时的任务,典型的工作速度在20MHz左右,但有些微处理器内核需要将该时钟频率内部分频,每条指令用多个时钟周期。例如,CISC微处理器在执行一条乘法指令时最多要用到25条简化的指令。

当今市场上已经有非常多的RISC微控制器,它们不仅能够实现单个时钟指令周期,而且功率非常低。例如Atmel的AVR 微控制器在1MHz时钟条件下能够获得1MIP的性能。由于有着如此强大的性能,几乎没有什么任务是微控制器不能完成的。这些微控制器的尺寸都非常小,品种从单个ALU和带通用I/O的存储器到多功能模拟和总线接口不一而足。

可编程逻辑器件由于能够满足低功率可重配置逻辑解决方案的要求,在微处理器市场上也颇有斩获。象CPLD(复杂可编程逻辑器件)这些可编程逻辑器件基本上也用于非常接近微处理器的应用领域,两者的重要区别是顺序与并行处理过程。微处理器执行指令时在多数情况下有分支例程,而 CPLD是并行处理输入和输出的,因此能够获得更高的处理速度和可预测的时序结果。对于以中断驱动的器件,这种方法能够显著地提高其工作速度。

CPLD的速度非常快,能使系统速度能够轻易达到并超过300MHz。CPLD的时序特性一般用纳秒(ns)或MHz描述(100MHz等于10ns,200MHz等于5ns)。今天的CPLD器件其输入到输出延时可小至3.0ns,速度相当于令人吃惊的385MHz!

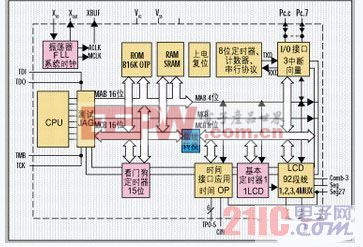

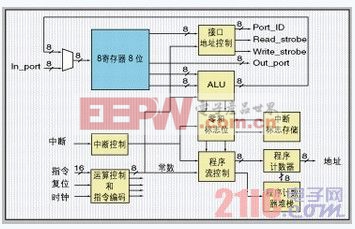

图1和图2给出了CPLD和微处理器的结构。所有CPLD器件都具有类似的这种结构,不同系列的器件只是在时钟特性、I/O标准和安全性等方面有所差别。虽然不同微处理器的结构也是相同的,但附加性能如时钟、ADC、DAC更能引人注意。

类似性

由于这些器件具有类似的功能,因此其性能也是类似的。它们都具有可编程性,通常都支持JTAG可测试性,能够用于类似的应用。表1详细给出了这样的类似性。一些公司为微控制器和嵌入式软核微控制器提供了在线的硬件调试器。

区别

但CPLD与微控制器还是有区别的。CPLD在系统上电时就能工作,没有启动过程。CPLD还具有非常精确的时序模型,由于能够进行并行的逻辑处理,因此可以提供更高的性能。但微控制器具有另外的特点,如A/D、专用的I/O总线端口和特殊引脚功能。微控制器与CPLD之间的主要区别如表2所示。

虽然微控制器能够提供更多的功能,但随之而来的是价格问题。有时微控制器上的功能也不一定能派上用场。如果设计要求是带50个GPIO的8通道 ADC,那么使用者还不得不支付那些不需要的功能的费用。这就需要认真地权衡功能与价格的矛盾。在某些情况下,仅使用设计要求的功能要比在更高器件成本上构筑成功的设计好得多,风险也比较小。

这二种器件在以安全为重的工业领域,如远程信息处理和工业设备中,还存在其它区别。质量认证依据的是测试故障机制,对于具有可预测性操作的逻辑器件来说是比较容易通过质量认证的,而微处理器则需要考虑复杂的状态。质量认证需根据一系列指令带来的可能输出数量来判定。由于分支指令在电压下跌或下降时通常会引起不可预知的操作,因此会使质量认证复杂化。而CPLD在电压恢复时可以再装载原始的逻辑配置,因此默认状态是可预测的,这种器件可以在预先定义的电压失效条件下工作。系统测试也比较方便,可以在CPLD中实现较难的中断处理仿真。

决策标准

比较两个具有相同功能却不同结构和产品类型的器件是相当有意思的。从某种角度看,为微处理器编写程序和为CPLD软核微处理器编写代码是相似的,二者都具有相同的操作流程。设计工程师可以向处理器或可再编程逻辑器件写汇编代码。对于可再编程逻辑器件来说,人们可以从各种系列、密度和功能的产品中作出选择。业界还为SPI、I2C和SMBus等可编程逻辑器件提供了许多参考设计。

值得注意的是,在复用和可移植性方面可编程逻辑器件具有更高的胜算把握。采用VHDL等高级语言的硬件分析通常要比来自不同厂商的不同处理器具有更好的可预测性。用VHDL可以将任意的可再编程逻辑器件作为目标,而微处理器中的一些特殊功能通常会随新的目标环境发生变化。而且芯片的更新或操作系统的修改都会迫使源代码的再次目标化。

两种都用?

某种程度上这两种器件具有互补性。对于与性能无关的任务,CPLD能够提供非常快速的引脚到引脚性能,并具有时序的可预测性,而微控制器能够提供诸如ADC、DAC和CAN、USB等专用总线接口性能。虽然这些性能会限制通用I/O的数量,但将CPLD用作微处理器端口扩展后就能解决这一问题。只具备必要功能的简化型微控制器的价格要比仅为满足I/O要求购买较大封装的器件便宜许多。CPLD能够提供的I/O数量少至32,多至250,并且能够在同一I/O封装中装配更多的逻辑。随着工艺尺寸的不断缩减,CPLD价格也在不断下降,因此设计工程师们在权衡性能与价格时会有更多的选择。

PicoBlaze介绍

PicoBlaze是8位的软核微控制器,支持8位数据总线和16位指令总线(如图3所示),是依据RSIC(精简指令集计算机)“哈佛结构”模型设计的,具有独立的数据和指令端口。可以用C语言编写的交叉编译器生成程序。PicoBlaze设计使用的是VHDL语言,并作了资料归档,因此随之的交叉汇编器能直接跟踪结构。

PicoBlaze在许多方面象是一台基于常数的机器。常数值可规定用于程序的以下方面:

1. ALU操作中使用的常数数值;

2. 常数端口地址,用于访问专门的某个信息或PicoBlaze方案之外的控制逻辑;

3. 控制程序执行顺序的常数地址值。

PicoBlaze指令集编码允许在任何指令字中定义常数。因此一个常数的使用不会给程序大小或程序的执行带来额外的开销,因此能有效地用全范围的 “虚执行”扩展简单指令集。所有指令的执行时间大约是2个时钟周期。当判断一个程序的执行时间时,特别是当嵌入到一个实时状态时,统一的执行速率是非常有益的。程序长度是256个指令,所有地址值定义为含在指令编码中的某个8位。固定的存储空间可以提升模块的一致性。必要时,可以扩展设计来支持更大的存储范围。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码