一种多通道时钟分频和触发延迟电路的设计

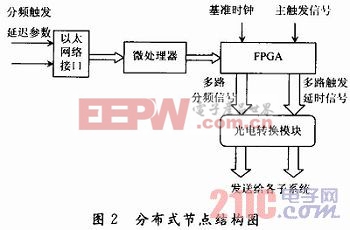

分布式节点是该中央定时触发系统的核心,而时钟分频和触发延迟也是分布式节点最重要的任务。分布式节点主要由微处理器和FPGA组成,外围由以太网络端口,光电转化模块等等组成。微处理器接收核心模块发送的分频系数和延迟参数,FPGA主要根据微处理器传输来的参数对输入的基准时钟进行相应的分频,并对核心模块发送的主触发信号进行延迟输出。时钟同步系统分布式节点结构如图2所示。

2 时钟分频设计

对基准时钟的整数分频主要分为等占空比偶数分频和等占空比奇数分频,它们的分频原理也是不同的,必须要分别对待。对于单通道偶数分频,设计比较简单,之前已经有很多这方面的研究,在此不再赘述。在本设计中,由于EAST定时触发系统需要多路分频信号,可以在程序设计的时候采用VHDL里面的类属参量和元件例化语句,类属参量Generic是一种端口界面常数,常以一种说明的形式放在实体或块结构体前的说明部分。类属参数映射的综合处理较简单,所有的参数配置都通过Generic map来传递,子模块内部只需要根据上层模块指定的参数进行综合即可。整数时钟分频电路需要在一个程序中可以同时对基准时钟进行奇数和偶数分频,所以在顶层文件中需要声明元件的语句格式如下:

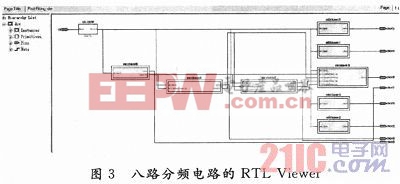

时钟分频设计的RTL Viewer,即在FPGA中所设计的电路原理图如图3所示,所有的计数分频模块都采用同样的基准时钟,以保证每路时序信号能够完全的同步。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码