类MIPS指令集的单周期处理器的实现

指令集

本文所设计的处理器使用MIPS指令集中的部分R类型指令(add、sub、and、or、slt),部分I类型指令(lw、sw)以及跳转类型指令beq作为其指令集。

处理器体系结构状态设计

MIPS处理器的体系结构状态由PC(程序计数器)、32位寄存器组和其它存储器所组成。处理器根据当前的体系结构状态,使用一些特定的数据执行一些特定的指令来产生一个新的体系结构状态。

数据通路设计

数据通路主要包括了R型指令以及I型指令的数据通路。其中R型指令的数据通路包括取指、译码、执行以及回写四个部分。I型指令的数据通路包括取指、译码、执行以及访存四个部分。

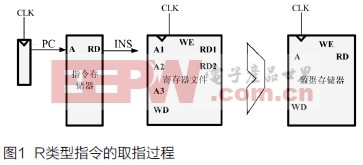

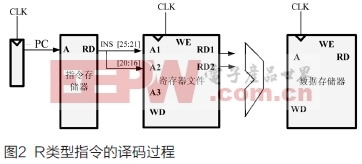

图1为R类型指令的取指过程:从PC中取出当前执行指令所在的地址PC值,送给指令存储器的访问地址端口A;由于指令存储器的读取不需要时钟沿,故当给出访问地址后,数据输出端口RD就直接输出地址相应的数据,也就是指令INS。图2为R类型指令的译码过程:首先,从指令存储器中读取出的指令中,第[25:21]位为R类型操作的第一个操作数在寄存器文件中的地址,第[20:16]位为R类型操作的第二个操作数在寄存器文件中的地址。寄存器文件根据A1和A2中给出的地址,读出两个源操作数的内容。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码