基于Nexys 3开发板的堆栈处理器的测试

前言

堆栈处理器是一种专门面向嵌入式控制领域的处理器,其所有执行过程均依赖于两个硬件支持的堆栈:执行数学表达式的数据堆栈(Data Stack)和保存子程序返回地址的返回堆栈(Return Stack),而不是大量的通用寄存器。堆栈处理器的特征使其相比较于RISC和CISC等通用寄存器处理器,更加适合应用于嵌入式实时控制领域。本文在上述背景下,介绍了一个堆栈处理器的IP核,给出了其在Digilent公司的Nexys 3开发板上的实现结果,以及使用ModelSim SE 6.5C仿真测试的结果。

堆栈处理器IP核简介

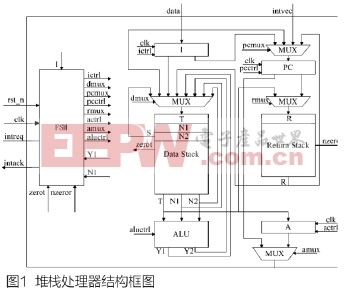

图1给出了堆栈处理器IP核的结构框图。从图中可以看出,本文的堆栈处理器IP核包含两个堆栈,一个是支持数据运算的数据堆栈,该堆栈由三个栈顶缓冲寄存器T、N1、N2以及一个深度为8的循环缓冲组成;另外一个是支持程序调用的返回堆栈,该堆栈由栈顶寄存器R以及一个深度为8的循环缓冲组成。处理器还包含一个程序计数器PC、一个指令寄存器I和一个地址寄存器A。数据运算则由ALU模块执行。处理器的所有操作都在有限状态机FSM控制下完成。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码