新一代芯片设计专享的定制数字版图

即便是在非关键网络,只要不妨碍反复作业的能力,自动化绕线都能够提高设计团队的生产力。而且,目前还无法呈现部分预先绕线与导引APR工具所需的精密间隔限制。所以,反而导致定制模块中不良的寄生效应,需要耗费人力的手工重新绕线与多次冗长的重新执行。

虽然自动化通常可以提高生产力,但是现在却使困难的制程变得更冗长,因为设计人员无法控制结果。事实上,对已经全部完成绕线的版图中关键网络的手工校对,通常比用手工从头开始绕线还要花费更多时间。设计团队得到一个结论,为了以更短时间实现最佳结果,需要能通过可控制式自动化而维护层次、连接与设计完整性的异质环境。

相互操作性节省时间

标准组织Silicon Integration Initiative(Si2)提供电子设计自动化(EDA)工具专属的可相互操作数据库,称为OpenAccess(OA),近年来已经成为定制设计的标准。OA有一项鲜为人知的功能OA Run Time Model(OA-RTM),可在OA上执行作为EDA工具专属的内存模型(in-memory model)。这表示,完全不同的工具可在同一时间、设计数据的同一内存代理上操作。运用OA-RTM的众多供货商的工具都可以如同单一供货商所提供的工具一般顺畅地配合作业。

运用OA-RTM,Pyxis Technology的全新高效能定制绕线器能够在Laker定制版图环境中作业。这个极大容量定制数字绕线器已经通过客户验证,能够在45nm和以下制程建立DRC-correct、DFM-aware的绕线;能够执行所有阶层的绕线而且是渐进式的,这表示,不必改变手工建立的既有关键网络。执行定制IC版图系统时,设计人员能够选择芯片面积,并且让整合式绕线器在这个限制条件下执行所有网络的绕线。强迫特定绕线通路的端口以及障碍(blockages)、变更与固定和既有的绕线全都由绕线器来辨识,不必数据转换或者将数据储存到磁盘。

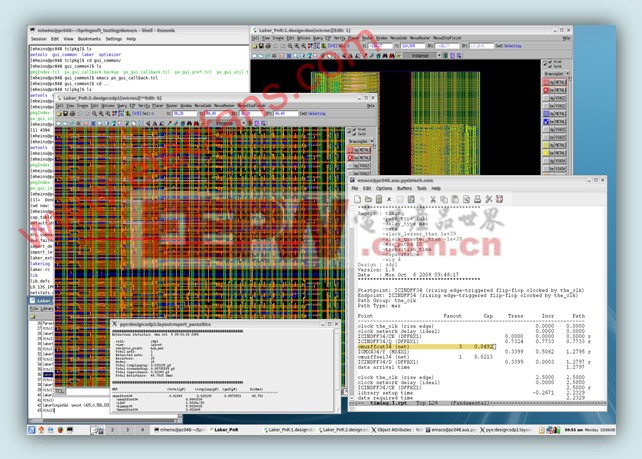

图4. 交互式环境实现假设性分析

运用这种具备相互操作性的解决方案,设计团队能够运用自动化定制IC版图系统与SDL方法,如同以前一样地建立版图。晶体管层的绕线由版图工具来执行,如同关键网络一般。或者,定义关键网络绕线的预先配线(pre-wires)可由版图编辑器来定义。以阶段式执行绕线,从关键网络开始,然后按照执行排序群组(阶层化),或整个区块,都只需几分钟时间即可一气呵成。

设计团队也能够充分运用定制绕线器的内建萃取与时序引擎,快速回馈寄生参数与样本时序。这样,工程师们能够判断绕线拓扑何时“已经足够好”了,以免布线过度。而且,这种定制流程的速度与可控制性非常实用,能够快速评估版图元素的放置,以实现最佳结果。绕线器也能够新增“虚拟填充(dummy fill)”(冗余金属,通常插入至版图中以提高数据密度,实现一致化与平坦化),帮助找出可能的破坏性寄生效应,以确保晶圆厂设置的虚拟充填不会导致意外问题。

结合这些功能与高度自动化的定制版图系统,设计团队与EDA供货商合作,建立了能够执行快速、反复“假设性”分析同时使版图与绕线优化的解决方案。由于能够反复地绕线、萃取、分析时序、修改与验证,设计团队能够降低实现更高效能目标所需的设计费用,同时也缩减功耗与面积 – 而所需时间远比以前单一版图所需的时间更短。

测试结果

涉及关键、高效能区块的特定测试以前需要6个星期的时间,才能够获得可接受的解决方案。这种区块的效能需求与面积和功耗需求互相冲突,非常难以圆满成功。为了确认绕线器的效能,既有的绕线会被移除。在版图编辑器中打平设计,整个区块会在几分钟内被自动绕线。模仿标准流程,会快速产生额外版本,在其中以手工运用版图编辑器进行关键网络的绕线,然后运用自动化绕线器来实现剩余网络。在自动化绕线程序中,不会改变任何关键网络,也不会有任何DRC违反。

刚开始的观念验证之后,设计团队证明一致的结果,通常需要3到6个星期才能够完工的大型、高效能定制数字区块,现在只需1个星期即可建立起来。这表示,设计团队可以腾出更多时间投入使定制区块的效能、面积与功耗优化的工作,最终让产品实现更高价值。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码