USB3.0中8b/10b编解码器的设计

2 8 b/10 b编码器的设计

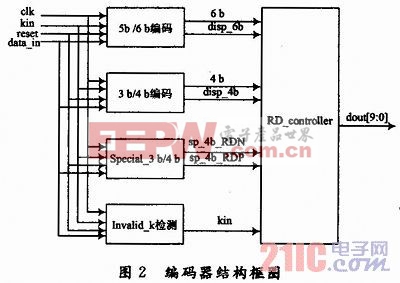

8b/10b编码器是把8 b数据输入拆成低5位和高3位分别进行5 b/6 b和3 b/4 b编码,根据编码表执行编码。因为其中有些特殊的3b/4 b编码,所以需要一个特殊3 b/4 b编码模块。编码后数据通过RD控制模块选择输出,并且把此时的RD状态反馈给下一轮编码。对于8 b控制输入,由于K控制编码只有12种有效,所以需要一个对无效K码的识别模块。因此,编码器分为5个模块:5 b/6 b编码、3 b/4 b编码、特殊3 b/4 b编码、无效K码检测、RD_controller,前4个部分在RD_controller的控制下进行并行编码,如图2所示。图中,kin为8 b控制输入,data_in为8 b数据输入。由于USB 3.0传输速度为5 Gb/s,编码器clk为500MHz。

5 b/6 b编码模块、3 b/4 b编码模块对输入的8 b数据输入分为低5位和高3位进行并行编码,输出6 b和4 b数据构成10 b编码,而输出disp_6b,disp_4b是6 b和4 b数据的不平衡度。

由于在8 b/10 b转换表中,8 b数据输入高3位为“111”、低五位分别为“01011”,“01101”,“01110”,“10001”,“10010”,“10100”时,输出的4 b是特殊情况,特殊3 b/4 b编码模块就是完成对这几种特殊情况输出,输出sp_4b_RDN和sp_4b_RDP是特殊编码的不

平衡度。

当8 b输入是控制K码时,控制码只有12种是有效的,无效K码检测模块就是检测输入的控制码是否有效,如果无效输出invalid_k=1,如果有效则输出invalid_k=0。

RD控制模块除了将编码后数据选择输出,主要是根据disp_6b,disp_4b,sp_4b_RDN和sp_4b_RDP来跟新当前RD值,并反馈到下一轮编码的RD输入,保持差分信号传输的直流平衡。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码