基于FPGA的卷积码编译码器

2 维特比译码器的设计

2.1 维特比译码器的原理

卷积码的译码一般采用维特比译码。维特比译码本质上是对长度为L的二进制序列的最佳译码,需要对可能发送的2L个不同的序列的2L条路径量度进行计算和比较,选取其中量度最小的一条作为幸存路径。其基础是基于网格图的描写,即对于不同的路径的量度进行比较,如某一节点上发出的某条路径已经不可能获得最大似然函数,那么就放弃这条路径,并在保存下来的路径中重新选择译码路径,一直到最后,复杂度较高。维特比译码器实际上对各个可能路径进行比较,比较原则是计算其路径的对数似然函数,而计算似然函数就是计算该路径与接收序列之间的汉明距(量度)。译码过程的操作可归纳为“加-比-选”3个部分。

实际的维特比译码中,译码几步后可能的路径便合为一条,因此,不必等全部译出后再输出,即译码一定长度后便可将已经相同的部分输出,这样做可以大量节省译码所需路径的存储空间。只要保证译码深度在5~10倍的约束长度之间就不影响译码效果,这就是所谓的“截尾译码”。

2.2 结构框图

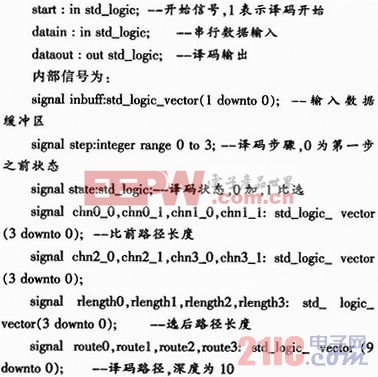

维特比译码器的结构框图如图2所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码