高速可扩展的Montgomery乘法器设计方案

3 性能分析与比较

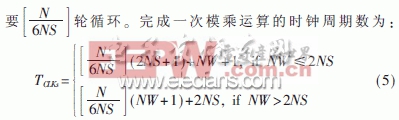

对于基为64的Montgomery乘法器,计算一次模乘运算的总时钟周期数时,需要考虑NW≤2NS和NW>2NS两种情况,NW代表操作数所含的字数。一个MMcell需要两个时钟周期的执行时间,因此一个字经过流水线的总时钟周期数是2NS+1。由于每次可处理6 bit,所以需

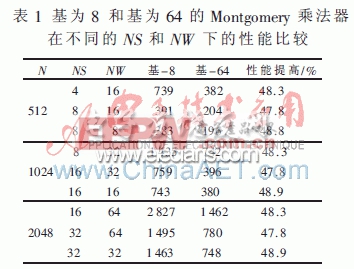

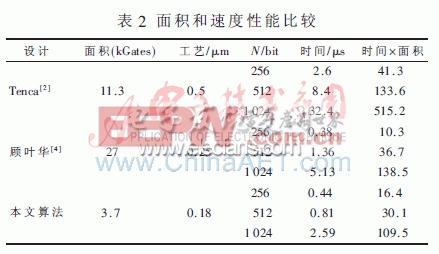

从表1可以看出,在不同条件下,本文的设计在性能上平均比Tenca的设计提高了48%。本文采用字长32 bit,级数NS=8实现基为64的Montgomery乘法器,且使用Verilog HDL语言实现上述设计,并使用ModelSim 对设计进行了仿真验证;基于SMIC 0.18 μm CMOS标准数字逻辑工艺,利用Design Compiler 进行了综合设计,结果显示频率达到251 MHz,面积为37 381门。

顾叶华在参考文献[4]中对Tenca提出的流水线结构进行了优化,提出了一种基为4的Montgomery乘法器方案。面积和速度的比较如表2所示。从表中可以看出,本设计在512 bit和1 024 bit下具有最小的时间×面积的值,综合性能最优。

本文对Tenca提出的基为8的可扩展Montgomery模乘器进行改进,采用了更高的基为64的设计,进一步减少了部分积的个数,缩短了运算时间。与Tenca在参考文献[2]中的设计相比,时钟周期数平均减少了48%,并且缩短了关键路径的延迟相比,综合性能具有明显地提高。

1

2

关键词: Montgomery 乘法器 设计方案

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码