超低抖动时钟合成器的设计挑战

除了PFD噪声,滤波器设置接近于10kHz时的VCO噪声峰值。剩下的主要问题是参考时钟噪声,不幸的是,40kHz以上优于模板性能不足以消除该噪声。所以,需要采用其它类型的振荡器来满足相噪要求,例如:OCXO。

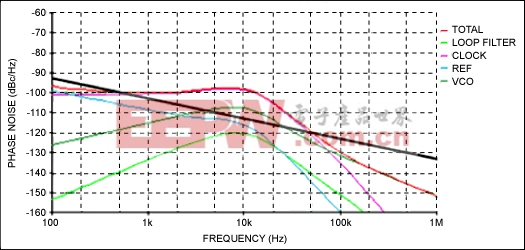

该设计的印刷电路板(PCB)可以适用三种或四种不同的XO引脚排列。图7给出了采用Vectron OCXO的仿真结果。即使考虑鉴相器噪声,最终的抖动为86.5fs。该抖动留出一定裕量给没有考虑的分频器噪声(该噪声应该没有明显的负面影响)和可能需要的放大器。

图7. 使用Vectron OXCO的仿真结果:4GHz下的相噪

结论

2GHz时达到100fs的抖动指标要比我们预计的更难实现。实验数据表明,利用一些标准的PLL电路可以达到这一目标。关键在于VCO和参考时钟的选择。实验证明,UMX的VCO具有一流的相噪性能。剩下的两个难题是:(1)选择噪声足够低的参考时钟;(2)选择合适的放大器。幸运的是,我们有很多器件可供选择,同样的电路布局可以适用于不同型号的引脚排列。放大器的选择比较困难,需要进一步分析以确定是否可以将其置于环路,还需考虑其噪声的影响。

¹考虑到两个单边带,文中在根号的内外均包含了系数2。总的噪声功率为SSB噪声功率的2倍,因此总的噪声电压应当等于SSB噪声电压。

²指的是单个元件,而不是模块。

³在1MHz附近具有很高的相位噪声,但是环路滤波器有助于衰减该噪声。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码