基于光纤通道的IEEE1394光信号传输系统设计

FPGA内部的工作过程说明如下:IEEE1394数据从16:32解复用器输出之后,进入IEEE1394数据拆分模块,产生对应于FC数据帧的SOF、DATA、CRC、EOF的数据段,生成符合FC帧格式的数据。在这之后,32:8复用模块将32 bit并行输入的数据复用成8 bit并行输出的数据。随后进入8 b/10 b编码模块,完成8 b/10 b的编码工作并以10 bit位宽,106.25 MHz的速率送入VSC7145串并/并串芯片,最后以1.062 5 Gbs的速率输出到SFP光收发模块,由光收发模块将电信号调制成光信号输出。

在RX接收部分,由光收发模块还原成的电信号通过VSC7145串并/并串芯片后以10 bit的并行数据形式输入到FPGA中,由8 b/10 b解码器解码,输出8 bit并行数据(在解码过程中,解码器可以通过判断码流的极性来判别是否在传输过程中出现误码)。8 b/10 b解码输出后的数据通过1个8:32解复用模块解复用成32 bit的并行数据,并行支路速率为26.562 5 MHz,随后32位并行数据通过FC帧检测提取模块,生成标识信号随路输出。在CRC校验/判决模块中,数据通过CRC位运算反映是否出现误码,并给出指示。在这之后,FC数据帧重组为IEEE1394数据帧,最后经由32:16复用模块将32 bit并行IEEE1394帧数据重新复用成16 bit并行数据,与53.12 MHz的随路信号一同送出FPGA芯片。

3 FPGA功能验证

本设计已在Xilinx Spartan3系列的Xc3s200中实现,并在Xilinx ISE 7.1仿真环境下进行了功能和时序仿真验证。采用伪随机序列发生器生成的伪随机代码模拟IEEE1394数据源,设定每1 000 Byte为一个数据包包长。

3.1 功能仿真结果

1)在发送端,IEEE1394数据包被拆封,重组成FC数据帧,并由8 b/10 b编码器编码后输出,如图6中仿真波形tx_dtout,和TX_encode_ dtout所示。

2)在接收端,FC帧结构被正确检测并提取,在CRC校验正确后重组成IEEE1394数据帧格式输出,如图7中仿真波形tx_dtout,crc32及rx_dtout所示。

经仿真测试,FPGA实现IEEE1394到FC数据帧格式的映射功能,各模块均正常工作,数据通信良好,无丢包现象。

3.2 时序仿真结果

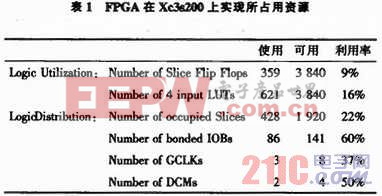

该设计在Xc3s200上实现后,FPGA所使用的资源如表1所示,整个系统资源占用率较低,最高运行速率能达到135.245 MHz,满足106.25 MHz的片上最高运行速率要求,设计达到了预期结果。

4 结束语

光纤通道具有支持多种上层传输协议的优点,本文在已有工作的基础上,利用FPAG,对所提出的IEEE1394到光纤通道的协议映射方案进行了硬件设计,通过FPGA功能仿真及时序仿真验证了所提方案的可行性。利用此FPGA协议转换模块,本文还设计了基于FC的IEEE1394光信号传输系统,给出了具体的硬件设计方案。目前,此系统的主要调试工作已完成,后续的工作将通过系统传输实验,对系统性能进行分析研究。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码