实现SOPC的嵌入式软硬件协同设计平台

2.2 电源电路设计

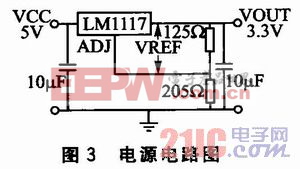

本设计采用了可调三端稳压器LM1117T-ADJ,可以将电压进行线性转换,电流为800 mA,3引脚的T0200封装。Cyclone系列FPGA上电的最大电流为300mA,该芯片可以满足要求。LM1117需要在输出与地之间接入电容以维持内部电路的稳定,输入与地之间也需要接入电容对输入信号进行滤波。具体的连接如图3所示。

2.3 Flash接口电路设计

Flash即闪速存储器,是一种在系统可电擦写的存储器。作为一种非易失性存储器,Flash主要有两个功能,一部分用来存储数据,另一部分存储专用程序。

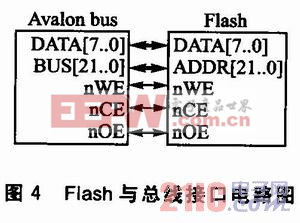

由于不同厂家的Flash的擦写时序往往不同,Niosll只支持部分常用的Flash,对于不支持的Flash类型,需要NiosII系统设计人员自己完成相关Flash擦写子程序的编写。本平台采用的AM29LV065 Flash存储器。采用48脚TSOP封装,8位数据宽度,工作电压为2.7~3.6V,读写操作都较一般Flash省电,仅需要单3 V电压即可完成在系统编程与擦除操作。

Flash选用的是22×8,即地址总线为22位,数据总线为8位,其连接关系如图4所示。

2.4 SDRAM接口电路设计

与Flash存储器不同,SDRAM不具有掉电保护数据的特性,但其操作都是由时钟作为同步。可以将其理解为一个电容,总是倾向于放电,为避免数据丢失,必须定时刷新(充电)。因此,要在系统中使用SDRAM,就要求微处理器具有刷新控制逻辑,或在系统中加入刷新控制逻辑电路。

在NiosII系统中,SDRAM主要用于存放运行程序和数据,并且其运行速度比Flash快很多。所以在SOPC系统中,当系统启动后,NiosII CPU首先从复位地址0x0处读取启动代码,在完成系统的初始化后,程序代码一般应调入SDRAM中运行,以提高系统的运行速度。平台使用的是hynix57V641620HGT,其存储容量为4Bank×1M×16位(64 Mb)。SDRAM与总线的连接关系如图5所示,其刷新频率是靠FPGA内的PLL经过相移来提供。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码