数字电视条件接收系统(CAS)设计技术解析

2. 带有软件冗余的内部SRAM

ARM7TDMI是一款没有内部高速缓存的CPU核,对于慢速的SRAM、FLASH存储器的只能空闲等待。即使采用了高速的外部SRAM,由于数据接口宽度和芯片与芯片之间的数据传输的延迟,也不能有效地用到高速CPU的全部性能;同时,大容量的高速SRAM价格昂贵,将会大大增加CAM系统的成本。从系统结构和成本方面考虑,我们决定在SM1658中嵌入一个256KB容量的SRAM,此SRAM容量可以满足相当部分CAM系统的应用需求。同时,我们的芯片也支持各种外部高速和低速SRAM,对于一些SRAM需求非常大的系统也可以满足要求。

SM1658内部实现的SRAM具有非常高的性能,可以以单时钟周期完成ARM的各种指令的操作,也就是当CPU在内部SRAM中进行取指或存取数据时不需要任何等待。我们在芯片生产出来后用对芯片内部的SRAM进行了CPU性能的基准测试,即使在非常高的频率下面,芯片也能获得与ARM7TDMI的IP核的理论计算值相同的水准,后面有测试的数据表格。

内嵌SRAM的最大问题是,对于芯片的成品率会产生影响。我们在电路功能设计、底层软件设计和应用系统上采取了一些有效的预防措施,大大减少系统对于有缺陷的SRAM的依赖性。这样,芯片的成品率可以大幅度提高。这样也就从系统角度降低了芯片的整体成本。

3. 可动态调整的时钟电路

在SM1658芯片的时钟设计中,我们还集成了一个可软件配置的时钟管理电路,称之为动态时钟电路。我们通过软件对芯片的时钟处理模块进行编程,既可以让芯片的工作时钟频率随着需要不断变化,降低芯片在轻任务负载下的功耗,又可以适应多种外部时钟源的输入,增加CAM系统在产品开发中的适应能力。

4. 高度灵活的智能卡接口

在SM1658的功能中,还包括一个高度灵活的智能卡接口。它是为了保证CA公司可以通过智能卡对用户收看节目进行授权和管理。

一般来讲,国际上大多数智能卡接口都是按照ISO7816标准来实现互连互通的。在很多的SoC芯片设计中,大家都采用了一个外部的智能卡接口芯片,例如TDA8004就是一个比较常用的智能卡接口芯片。但是采用一个外接的芯片,其系统的可靠性会降低而成本会比较高,我们希望设计一个成本和性能最优的系统,通过电路设计完全省略掉此外部接口芯片。

首先,我们在此接口模块的设计中,按照ISO7816的标准,将全部的状态和控制方式都完成。比如,针对A类、B类智能卡卡的不同电源电气指标要求的设计;针对T0通讯协议与其他通讯协议不同的错误处理的设计;还有针对某些私有的智能卡的特殊协议要求等。这些都可以通过在芯片的驱动软件上进行配置,配合少量的简单外部器件来完成。其次,针对智能卡接口要求的ESD要求和不同使用环境中的差别,我们设计了不同的外部电路来配合芯片的内部控制。同时,我们对芯片的各个接口管脚的逻辑特性进行了不同条件下的独立配置,可以最大程度地减小对外部电路的要求。

图3:智能卡模块系统软件功能框图。

在标准的使用情况下,SM1658芯片可以不需要任何外部有源器件就完成智能卡接口的功能,而且抗ESD的能力可以保证大于4,000V。

5. 内嵌高速DVB通用解扰算法

通用加扰算法是DVB标准组织推荐的对于TS流的标准加扰算法。目前,在欧洲的数字广播节目中普遍采用了这个算法。我国目前商业化的CA中,TS节目的加扰也基本上是采用的这个算法。因此,我们向DVB组织申请了此算法的授权,并以固核的模式嵌入到了我们的SM1658芯片中。

在此固核的设计中充分考虑到了芯片对将来可能出现的多路高清节目的适应能力,将此解扰模块的处理能力设计到了175Mbps,可以满足同时处理2路高清节目流或4路标清节目流的水平。

6.高性能的TS流处理引擎

在SM1658中,我们还设计了一套TS流处理引擎,用来对CI接口传送过来的TS流进行整形、过滤、提取特定数据、回送解扰后的节目流等。在此引擎中,我们设计了64个PID过滤器和16个SECTION过滤器,根据不同的配置状态,此引擎可以完成对TS流7种不同的路由功能。

SM1658性能指标

1. 最高工作时钟频率

SM1658芯片采用了中芯国际的0.18um的标准逻辑CMOS工艺生产。在SM1658的芯片设计中,我们采用了ARTISAN的0.18um工艺库和MC编译器,采用了SYNOPSYS的DC综合工具进行综合,并采用最新的CADENCE的后端设计工具ENCOUNTER进行布局布线和SI分析,通过对芯片内部总线、存储器和关键路径模块进行优化,使芯片的时序基本上达到了ARM7TDMI IP核手册上测试的标准性能。

我们完成流片后对芯片进行了最高时钟频率的测试。常温下以1.8V的核心电压和3.3V的IO口电压条件,SM1658可以工作在125MHz~135MHz的频率下,这可能是已经商用化的ARM7TDMI类芯片的最高工作频率了。

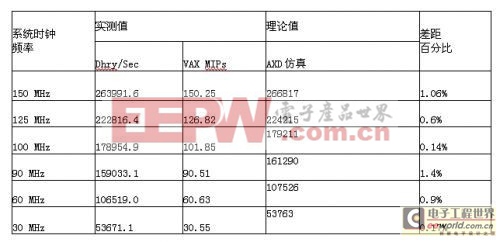

由于我们对芯片的总线、内部存储器进行了优化,为了证实此优化效果。我们对于芯片的最高运算能力进行了基准测试。我们的测试程序使用的是ARM公司提供的参考测试程序Dhrystone2.1(C语言编写),以性能最优的方式进行编译。该测试程序在芯片的内部SRAM中运行。下表是我们的测试结果以及与软件仿真测试结果的比较。可以看到,我们的芯片在最高性能时的执行效率已经基本达到了ARM7TDMI的最好的指标,这也说明,我们的设计是非常优化的。

表1:SM1658的最高运算能力基准测试结果。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码