数字下变频器中坐标变换模块的ASIC实现

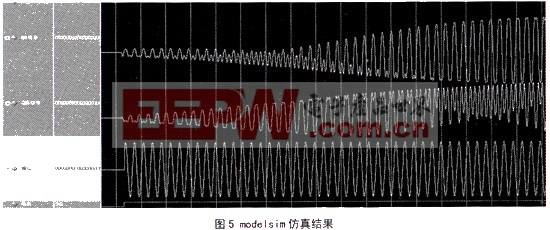

2.3 使用modeIsim仿真的结果

图5是当输入激励为I路:sin(sin2πf);Q路:COS(COS2πf)时的modelsim仿真结果,由图中可以看出坐标变换得出的相位值是一个标准正弦信号,幅度值为恒定值,幅度相位完全正确。

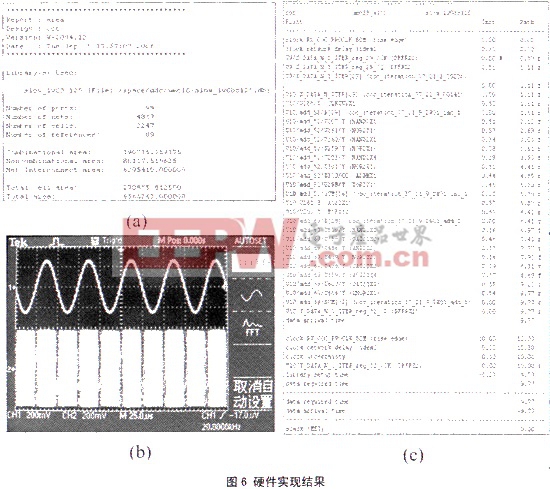

2.4 硬件实现结果

在硬件实现时,用verilog语言对坐标变换模块进行描述,为满足DDC的精度要求进行了18次迭代,并用DC基于UMC0.18μm的库进行了综合,硬件实现结果如图6所示。

图6(a)是DC综合后的面积报告,图6(c)是关键路径的时序报告,综合后的最大路径延时为9.77ns,完全可以满足本模块数字下变频器100MHz的处理速度要求,综合出的单元(cell)的总面积仅为0.27。图6(b)是该设计在FPGA上验证的结果,该DDC的工作频率为80MHz,通道2为输入的基带信号频率20kHz,载波频率5MHz,频偏200KHz的FM信号,通道1是通过DDC下变频后交给坐标变化模块的I,O两路信号求出的相位信息,即频率为20kHz的正弦信号,由图可知该没计实现了坐标变换功能。

3 结论

使用CORDIC算法,并用流水结构实现幅度相位的求取可以获得较高的处理速度,增加迭代次数可以获得更高的处理精度,但会耗费较多的资源,在设计时应根据需要,合理的确定迭代次数。该设计已成功应用于高速数字下变频芯片中。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码