基于ARM和FPGA的便携人工地震数据采集系统设计

ENTITY spi IS

PORT ( CLK :in STD_LOGIC;--4.096 MHz

CLK40 :in STD_LOGIC;--40 MHz

SYNC :out STD_LOGIC;--PINMODE模式下,

使用复位信号同步数据采集信号

DOUT1 :in STD_LOGIC;

SCLK1 :out STD_LOGIC;--第一通道的

ADS1281模数转换器的SPI时钟

nDRDY1,nDRDY2,nDRDY3:in STD_LOGIC;

--ADS1281数据就绪等待采集信号

spi_clk :out STD_LOGIC;--扩展SPI时钟

spi_mosi :out STD_LOGIC;--扩展SPI主机

发送从机接收数据信号线

spi_cs1 :out STD_LOGIC;--扩展SPI片选

信号

EINT1,EINT2:out STD_LOGIC;--FIFO半满数

据采集中断信号AD_INT,

和DAC数据请求中断信号INT

ENABLE1,A2,A3,A4,A5:in STD_LOGIC;

DATA:inout STD_LOGIC_VECTOR(15 downto 0);

--ARM处理器数据总线

led_drv:out STD_LOGIC;--LED状态指示

PPS_interrupt:out STD_LOGIC;--1 Hz,

GPS秒脉冲

nRESET:in STD_LOGIC;

GPS_IRIGL:in STD_LOGIC;--IRIG码读写

nRD:in STD_LOGIC;--ARM读

nWR:in STD_LOGIC;--ARM写

nCS:in STD_LOGIC);--ARM片选

END spi;

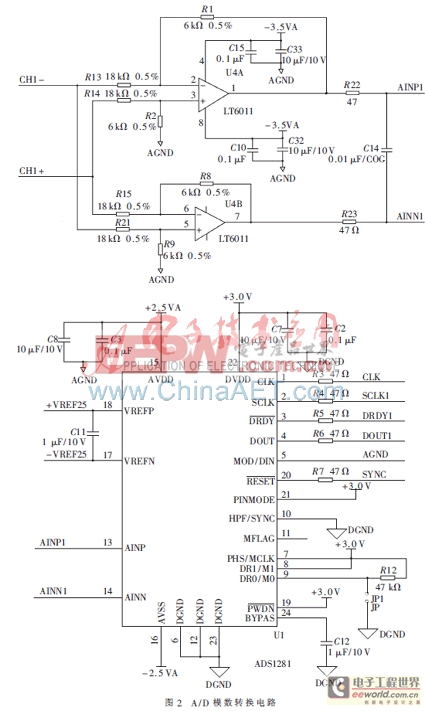

1.2 A/D数据采集通道

A/D转换器采用TI公司的ADS1281。该A/D转换器具有高分辨率、高精度特性,内置4阶稳定的ΔΣ调制器,可配置SINC、FIR和IIR滤波器,数据率250 S/s~4 KS/s,特别适合地震数据观测环境。在本设计中,模拟地动波形信号经差分放大后输入到AD1281的AINP和AINN端。SCLK由FPGA分频产生的1.024 MHz的时钟驱动,用于串行输出A/D数据到FPGA FIFO。当A/D完成数据转化后,CH1_DRDY拉低向FPGA表示数据准备就绪,等待读取。CH1_ DOUT连接至FPGA的DOUT1端口,用于数据到FPGA FIFO的串行传输。AD_CLK由4.096 MHz时钟驱动,是A/D的工作时钟。A/D转换原理电路如图2所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码