利用P89C669的23 b的线性地址并采用CPLD外部扩展

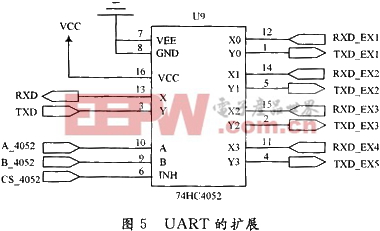

在本设计中,共需要得到设备选择信号如SRAM芯片M68AF127B的片选CS_RAM,2个FLASH ROM芯片SST29SF040的片选CS_ROM0,CS_ROM1,模拟多路选择器SN74LV4052的使能信号线CS_4052,另外还有一些控制信号线,这里就不一一介绍。

实际上,P2口引入CPLD,就P89C669的23 b地址线而言,用来地址译码和少量的控制信号等主要是利用最高的几位,在本设计中,由于SST29SF040用到地址线A0~A18,所以CPLD的地址译码处理只能是利用剩下的A19~A22,这将在下文的CPLD的译码单元可以看到。

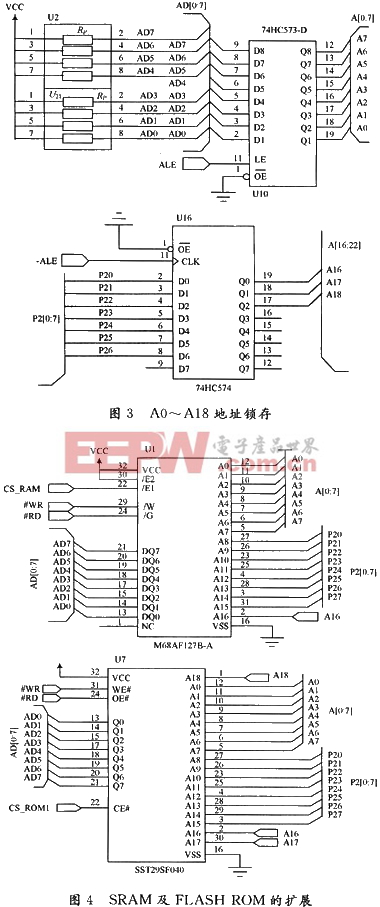

A0~A7低地址采用74HC573进行锁存,A16~A18地址内容采用74HC574进行锁存,如图3所示。

M68AF127B,SST29SF040,74HCA052的功能连接图如图4所示,74HC4052用于UART口的扩展,如图5所示。

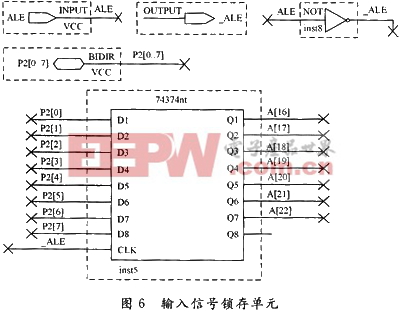

3 EPM7032S的逻辑设计

CPLD的设计采用原理图的方法进行设计,简便快捷,如图6所示,采用74374模块锁存P2口的输入信号,ALE反向后得到_ALE作为74374的锁存时钟线输入。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码