基于FPGA的视频信号发生器设计

其中图像的采集是从行同步上升沿开始后,按像素时钟采集的。

本文根据数字视频产生所需的各要素进行信号发生器的设计。主要通过FPGA产生行同步信号、帧同步信号、像素时钟;通过单片机+串口通信模块实现目标参数的更改,并把更改后的参数传递给FPGA,供FPGA产生相应运动的视频信号;通过视频制式转换模块把FPGA生成的视频数据及视频控制信号转换成LVDS和CamerLink制式的数字视频信号。

2 FPGA控制模块

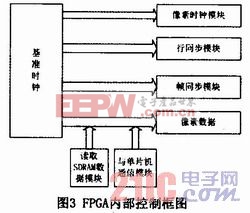

FPGA具有高集成度、高可靠性以及开发工具智能化等特点,目前逐步成为复杂数字电路设计的理想首选。此外FPGA可以通过编程实现硬件的逻辑功能,大大减少了硬件设计的复杂程度。因此本文以FPGA为核心器件产生视频信号,这里选用ALTERA公司的SycloncII系列的EP2C8 F25618N,采用VHDL语言编程生成与数字视频有关的各个信号,与单片机通信接收视频修改参数的模块及得到SDRAM内部图像的模块。其结构框图如图3所示。

信号发生器上电后,FPGA通过与单片机通信的模块得到初始视频各项参数,根据参数进行目标大小、目标灰度、目标运动速度、背景灰度的设置,然后根据各项设置产生视频数据,FPGA帧同步模块、行同步模块、像素时钟模块分别产生帧同步、行同步、像素时钟,图像数据按以上控制信号从FPGA中发送出去。

在本文中FPGA各功能模块根据基准时钟生成帧同步、行同步、像素时钟。这里以50M时钟为基准时钟信号,根据图像处理平台对输入信号的要求,设计的帧同步高电平占33ms,低电平占1.2ms,行同步高电平占35 μm,低电平占8.4μm。这里把50M基准时钟输入像素时钟模块经过锁相后依然以50M的时钟频率输出,作为像素时钟。由于一行较多,可在程序中进行限位,控制每行像素数。像素的产生主要有两种方式,一种是通过与单片机通信得到目标像素灰度及背景像素灰度,根据这两种灰度产生像素数据。另一种方式是通过从连接在FPGA上的SDRAM内读出图像作为背景,从与单片机通信得到目标灰度,共同形成像素数据。

2.1 单片机控制模块及通信模块

在本设计中单片机作为通信管理芯片。它主要实现与计算机的通信,更改信号发生器所产生信号的各个参数,把各个参数经过整合送给FPGA,以便FPGA根据参数控制目标的运动速度、目标大小、目标灰度及背景灰度。为了保证信号发生器能够方便地和计算连接,实现人机交互,实时更改产生的视频信号,并且从通信稳定可靠出发,这里采用RS232通信接口。但是因为计算机每次发的数据较多,这里没有直接应用电平转换芯片把计算机和单片机的串口连在一起,而是通过一片16C650把电平转换芯片和单片机连在一起,这样的好处在于16C650内部具有32字节的FIFO,可起到数据缓存的作用,使单片机能够稳定可靠地接收数据。

2.2 视频制式转换模块

因为FPGA产生的视频信号为TTL电平,而目前数字视频信号以LVDS制式和CamerLink制式为主,因此需要进行电平转换。这里主要采用把FPGA产生的TTL电平的数字视频信号接入SN75LVDS387得到LVDS制式的视频信号,同时可把该TTL数字信号接入DS90CR285得到CamerLink制式信号。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码