基于ADS仿真的X波段二倍频器设计

平行耦合滤波器的每一节耦合线电路均可等效为一个导纳倒相器和在两端连接有电长度特性导纳为Yo的传输线组合,这里采用第一种形式耦合电路,其等效电路如图7所示。

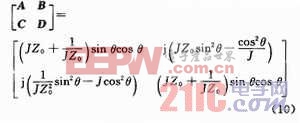

分析时采用传输线的A,B,C,D矩阵来计算,导纳倒相器可视为特征阻抗为1/J的1/4波长传输线,故可得出每个耦合电路的等效电路A,B,C,D矩阵如下:

其奇偶模阻抗为:

![]()

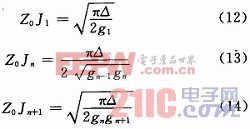

上面是对于单个耦合电路而言,考虑n+1节耦合电路级联组成的带通滤波器,通过单个耦合电路奇偶模阻抗可推得n+1节耦合电路级联带通滤波器的奇偶模特征阻抗如式(12),式(13),式(14)所示。

根据上述公式即可求出n+1节耦合线级联带通滤波器奇偶模特征阻抗,要注意的是其阻带特性不是十分理想,特别是在2ωo的衰减极点处,稍有失谐便可能产生寄生通带,因此设计时必须进行精心仿真和调试。

设计之初要考虑滤波器级数n的选择,因为其选择会直接影响滤波器插损和带外特性,此外还要在分析滤波器通带及带外特性的基础上对滤波器进行理论估算。对于相对带宽较窄时可利用滤波器的近似设计方法来计算其结果,这样处理虽然简化了设计和计算过程,但得到的结果往往存在精度不高的问题。利用先进的ADS仿真软件对其进行正确的建模,可以对理论计算结果反复的仿真和优化,直到结果满足指标为止。

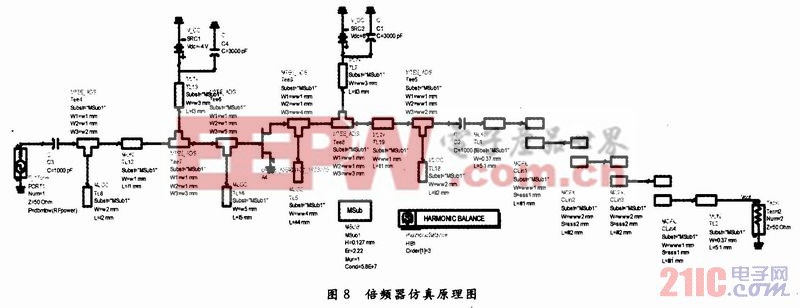

2.5 倍频电路设计与优化

将优化后的参数代入如图8所示的倍频仿真电路,为了便于观察激励电平影响,选用ADS中的单音频率源作为输入端,其阻抗可以人为设定,根据倍频器的外围环境阻抗决定此时阻抗为50 Ω。为保证仿真优化结果接近实际值,必须考虑建模的精确性。比如器件封装的影响,对电路中传输线和匹配网络建模要尽量接近实际,比如重点考虑微带突变节、十字节、开短路短截线的设计。

介质基板材料应选用表面光滑度高、韧性好、硬度高的低损耗微波介质材料,尽量选用小尺寸电路以减小传输线损耗,另外还要考虑所选基板介电常数随环境温度及湿度变化要小,除了考虑基板厚度、相对介电常数以外,还包括介质损耗角正切等参数。综合考虑成本及上述因素后,整个电路制作在介电常数εr=2.22,厚度H=0.127 mm的Rogers RT/duroid 5880基板上。

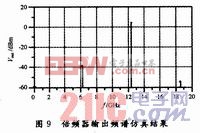

在保证稳定性的前提下仔细设计输入/输出匹配及偏置电路,得到匹配网络初值,再利用ADS的谐波平衡分析方法对电路进行仿真和优化,仿真电路如图8所示。运用软件进行多次的仿真优化来选择合适的激励功率,由于所选GaAsFET工作在1.5~26.5 GHz频段,基波分量仍占主导地位,同时还需进一步滤除无用谐波以得到理想倍频效果。这里主要关心二次谐波输出,由于倍频器产生的谐波幅度并不完全与激励功率成正比,综合考虑倍频损耗及基波、三次谐波的影响,选择最佳变频损耗对应激励功率为10 dBm,中心频点12.4 GHz的仿真优化输出频谱特性如图9所示。从总体仿真结果来看,倍频器可获得理想的变频损耗,同时对于基波和无用谐波的抑制效果良好,符合设计要求。

3 结语

本文讨论了一种GaAsFET倍频器的设计,介绍了设计的具体流程和方法,并充分利用ADS仿真软件对倍频器进行优化设计,省去了复杂的理论分析计算,大大简化了设计过程,对倍频器的CAD设计具有很大的现实意义。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码