用LatticeXP FPGA 桥接吉比特媒体独立接口

● LatticeXP工作频率>125MHz

● 采用LatticeXP中的HSTL I/O

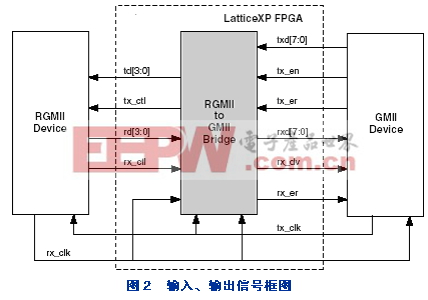

RGMII至GMII的桥接以双倍数据率(DDR)传送数据。双倍数据率允许在时钟的上升沿和下降沿传送数据,因此使数据吞吐量增加了一倍。LatticeXP FPGA的每个PIO都有I/O移位寄存器,对它们编程使得在时钟的两个边沿传送数据。使实现这种接口的器件的引脚数从22个减少到12个。电路的框图如图2所示。RGMII器件和GMII器件在LatticeXP器件的两边。

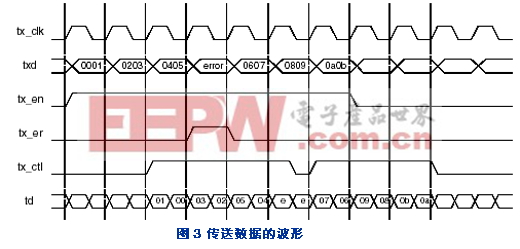

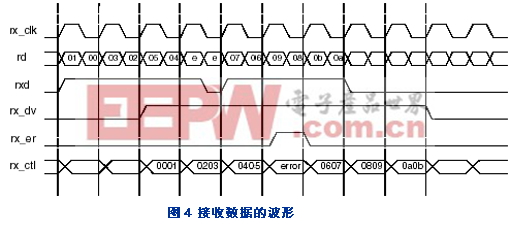

图中tx_clk为发送时钟。txd[7:0]从GMII器件传送数据。td[3:0]传送数据至RGMII器件,传送3:0在发送时钟txclk的上升沿。传送7:4在发送时钟txclk的下降沿。tx_ctl是控制信号,用于传送其它的Tx信号到RGMII。tx_en传送使能信号,高电平有效。tx_er传送数据出错信号,。rx_clk为接收时钟。rd[3:0]为来自RGMII器件的接收数据输入端,位3:0在接收时钟rx_clk的上升沿,位7:4在接收时钟rx_clk的下降沿。rxd[7:0]接收数据输出至GMII器件。rx_dv是接收数据使能信号,高电平有效。rx_er接收数据出错信号,高电平有效。传送数据和接收数据的时序波形分别如图3和图4所示。

数据和控制信息的复用是利用了时钟信号的两个边沿,在时钟信号的上升沿发送低4位,在时钟信号的下降沿发送高4位。正是采用LatticeXP FPGA的特性,能够以 双倍数据率传送数据,实现RGMII与GMII的桥接功能。

1

2

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码