基于DSP离散频率编码雷达信号的实现

3 波形发生

3.1 芯片简介

TMS320F28335(TI)32位浮点数字信号处理器(DSP)芯片,拥有工作频率达150 MHz的32位DSP内核处理器,采用哈佛总线结构。程序读总线有22根地址线和32根数据线,数据读写总线都是32位。

DAC7724为4通道、12位分辨率、±10 V信号量程,建立时间10μs,±15 V供电的D/A转换器。理想的输入数字量与输出模拟量之间的关系如下:

式中:N为数字量输入;VOUT为模拟输出;VREFL为低参考电压;VREFH为高参考电压。

3.2 软件设计

3.2.1 设计思路

首先执行局部搜索算法,得到频率编码序列数组n[L,N];然后启动定时器0,设置死循环等待中断;在中断服务子程序中将各时刻信号s的幅值送至DAC输出。

3.2.2 设计流程

中断服务子程序中可通过拨码开关控制波形频率个数,即从频率编码数组的N个频率中选取1个,2个或全部频率,以实现实时的单基、双基、多基间转换。其设计流程如图5所示。

3.2.3 波形输出具体实现说明

中断服务子程序中的波形输出比较复杂,有必要作详细说明。

(1)确定TIMER0的中断周期prd_isr;

(2)确定在一个脉宽tb内输出的点数num=tb/prd_isr;

(3)当中断次数countnum时,波形频率不变,信号值如下:

![]()

将其值进行D/A转换,从第i个通道输出,每转换一次count加1;当中断次数count>num时,count置零,同时j加1,转到下一个频率。

3.3 结果波形

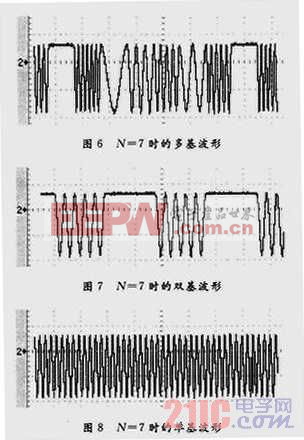

N=7时的多基、双基、单基结果波形如图6~图8所示。

3.4 结果分析

图6~图8中波形的频率按照求得的频率编码n[i][j](0≤iL,0≤jN)变化,且利用拨码开关实现了单、双、多基间的转换,达到设计要求。

4 结论

利用Matlab进行了局部搜索算法的验证,并给出了仿真结果,结果表明解得的离散频率编码序列集合具有良好自相关和互相关性;然后用DSP实现波形发生系统,得到的结果符合预期设计要求。

本文给出了离散频率编码雷达信号的实际产生方法,对实际应用有较高的借鉴价值。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码