高精度DDFS信号源FPGA实现

1)相位累加器(地址发生单元) 设计思路为根据输入的Step值,计算出1/4周期采样的点数m,然后在时钟作用下进行计数,当计数值达m个时,说明一个象限内已经取完点,此时象限控制字自加1,计数变量重新置零,此时依次产生了如下(0,Step,…,(m-1)Step)的30位二进制地址。截取此地址位的高10位即可用于对ROM空间的寻址。根据正弦信号的特点,下一象限产生的地址应该为:((m-1)Step,(m-2)Ste-p,…,0),依此类推。且象限控制字自加。

2)ROM存储单元 ROM存储单元的数据可以通过Matlab进行计算获得,并将其存储为dds_sin.mif。也可采用其他高级语言来获得ROM存储数据。

3)补码转换电路 (0,π)数据直接输出,(π,2π)象限的数据应进补码运算。对此补码电路稍作修改,即可同时输出相位正好相反的两路正弦信号。

4)数据延时单元 为了使地址单元输出的象限控制字等与异步ROM配合工作,应对相应的数据进行延时,以保证输出数据的正确。本设计中对相位控制字延了一个时钟周期。

3 DDFS设计模块性能及所占资源分析

1)DDFS模块时序分析 首先应当分析DDFS模块的最大时钟频率fmax,因为它决定着系统能否工作在150 MHz或更高的时钟频率。通过Qu-artusII6.0自带的Timing Analyzer Tools时序分析,本设计中的DDFS模块的fmax=179.18 MHz,高于150 MHz。故本设计理论上可输出的正弦信号的最高频率可达11.198 MHz。

2)DDFS模块资源分析 本设计使用的是FPGA为Ahem公司的CycloneⅡ系列芯片EP2C5Q208C8,所设计的DDFS模块所占片上资源逻辑单元仅为2%,所占的数据存储空间为12 288 bits,约占总的数据存储空间119 808 bits的10%。可见,通过对ROM存储表进行数据后,DDFS模块所占片存储资源较少。因此,FPGA上ROM资源允许调用若干DDFS模块来完成各种功能模块,如2-PSK、2-FSK、2-ASK等数字调制。

4 系统性能仿真与测试

以DDFS模块为基础,本设计实现了两组反相的正弦信号、余弦信号、三角波信号、锯齿波、2-PSK、2-FSK、2-ASK等数字调制信号、扫频及任意次波形输出等功能。

在本设计中,仿真主要通过QuartusII6.0自带的Simulator Tool来进行数据仿真。从仿真图上可验证该设计的正确性。同时,通过Qu-artusII6.0自带的Signal TapⅡ逻辑分析仪来进行逻辑功能的硬件验证。

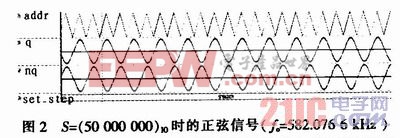

1)基本正弦信号输出 在本设计中同时产生两组信号,一组为正弦信号,另一组与之反相。图2是步进长度设定为(50 000 000)10时的正弦信号Signal Tap II采样图,其频率分别为fo=582.076 6 kHz。此时输出信号为可产生的最高频率。从所获得的输出信号的波形上看,频率较低时,曲线稳定且光滑;频率较高时,波形失真也并不大,可以通过后级滤波网络进行波形的进一步平滑。且频率稳定度相当高。

在外部时钟50 MHz的频率下,可以获得的最高频率约为3.125 MHz,最低频率及频率步进可以低至11.64 MHz。当对外部时钟信号倍频至150 MHz后,最高输出频率可以达到9.375 MHz,最低频率及频率步进可以低至34.925 MHz。进一步提高频率及模块性能,能获得更大频率范围的信号。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码