基于FPGA的高性能DAC芯片测试与研究

2.3 软件设计

软件代码采用硬件描述语言Verilog实现。FPGA产生待测信号包括Test(全零、全一等)、Ladder(阶梯波)和Sin(正弦波)。其中Test信号用于测试DAC芯片的静态特性参数失调误差和增益误差,Ladder信号用于测试DNL和INL,Sin信号用于测试动态特性参数SNR、SINAD、ENOB、THD和SFDR。

数据分析和计算过程主要通过Matlab 软件实现。DAC 芯片输入全零和全一信号,可计算出失调误差和增益误差;使用阶梯波信号测试INL 和DNL 时,为了测试精确度,将12位输入数据分成高中低各四个位进行测试。DAC 的动态特性参数测试采用快速傅里叶变换的方法,将Signal tap II 工具取出数据经过FFT 和其他运算,得到SNR、SINAD、ENOB、THD 和SFDR 等动态特性参数,它们可以全面地反映DAC 的动态特性,这里精确到14 阶谐波。

3 测试结果

Test 信号测试:DAC输入全一状态的输出电压为760 mV,输入全零状态的输出电压为276 uV,经过Matlab 计算,失调误差是0.036%,增益误差是3.63%。

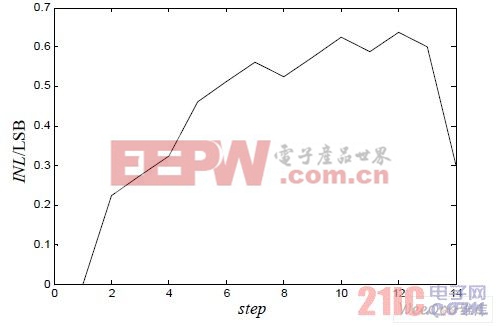

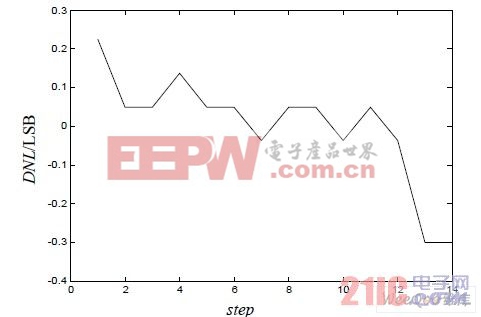

Ladder 信号测试:在计算INL 和DNL 时,DAC 输入高中低各四个位的测试原理相同,以中四位为例来介绍。n=12,i 从24~28 位变化,用1LSB 来表示,测定输出的15 次(Step)阶梯波,转换成电压值,部分数据如表1 所示,每列数据分别表示阶数、测试最小值、测试最大值、测试平均值、理想数值以及考虑小电流影响后最终电压值。使用Matlab 软件分析数据后得到INL 和DNL 曲线如图2 和图3 所示。

表1 15 次阶梯波电压值

图2 INL 分析曲线

图3 DNL 分析曲线

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码