基于FPGA的IRTG-B码编解码器的设计与实现

2 IRIG-B编码模块的设计

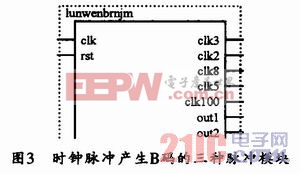

2.1 时钟脉冲产生模块设计

为了达到系统所要求的精度,使频率较为稳定,设计时可用更高的频率作为时钟分频链的第一主时钟。这里采用锁相环实现倍频方法来提供所需的频率,可选用Quartus II软件中宏功能库中自带的PLL来提高整体的运算速度,同时也能合理的进行资源综合。实事上,使用基本的宏定义模块可以明显地提高用户的设计开发时间。时钟脉冲产生电路是IRIG-B码产生器不可缺少的单元,该电路主要由几个分频器级联和一些逻辑门组成。

电路中的数字分频器可对外部提供的频率进行分频,以产生系统所需时序脉冲和B码的三种基本编码形式脉冲,其宽度(高电平)分别为2ms、5 ms、8 ms,频率为100Hz的脉冲信号:其中第一种是高电平为2 ms、低电平为8 ms的脉冲(代表逻辑“0”);第二种是高、低电平均为5 ms的脉冲(代表逻辑“1”);第三种是高电平为8ms、低电平为2 ms的脉冲(作为位置识别标志和参考码元)。Quartus II软件下的仿真模块结果如图3所示。

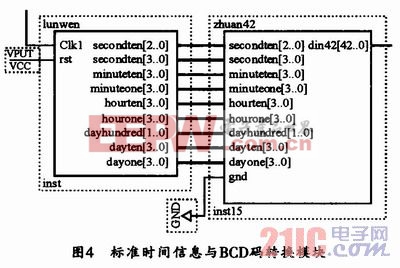

2.2 标准时间信息和BCD码转换模块设计

该模块由百分秒计数器、秒计数器、分计数器、时计数器和天计数器级连而成。它可对预置的时间进行秒加一,每隔一秒对时间信息刷新一次,从而形成动态BCD码,并使时间信息符合IRIG-B码的格式。标准时间信息和BCD码转换模块如图4所示。

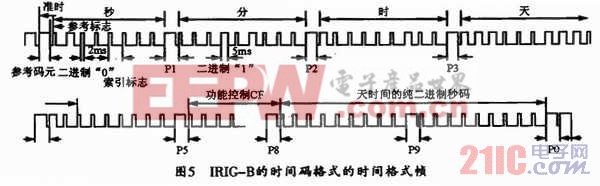

2.3 IRIG-B码DC格式的生成

IRIG-B(DC)时间码格式的时间格式帧从帧参考标志开始,因此,连续两个8ms宽脉冲中的第二个8ms脉冲的前沿为秒的准时点,该点标志着一个时间格式帧的开始,称为参考码元。从第二个8ms开始,分别为第1、2、…、99、0个码元。B码时间格式中含有秒、分、时、天等信息,其位置在P0~P5间。时间信息中,高电平用5ms脉冲表示,低电平用2 ms脉冲表示,其中秒信息占用第2、3、4、5、7、8、9码元;分信息占用第11、12、13、14、16、17码元;时信息占用第20、21、22、24、26、27码元;天信息占用第31、32、33、34、36、37、38、38、41、42码元;P6~P10包含其他控制信息(这里没有应用)。另外,第6、15、25、35、…、95码元为索引标志,用2ms脉冲宽度表示,固定为“0”。时、分、秒均用相应BCD码表示,低位在前,高位在后,个位在前,十位、百位在后。图5所示是IRIG-B时间码的格式帧示意图。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码