数字控制振荡器(NCO)的FPGA实现

相位累加器可完成相位累加,即每来1个时钟就累加1次φ=φ+△φ,且采用流水线方式工作。本设计采用QUARTUS II中IP核自带的一种32位累加器来实现相位的累加。

逻辑转换完成后,可采用小表结构功能块把相位累加器产生的最高2位信号转换为地址控制信号和象限转换控制信号。其中地址控制信号是根据最高两位信号来控制地址从0开始递增方式产生还是从2L开始以递减方式产生。

正弦表是每来一个时钟输出一个大于零的正弦值数据,这些数据可作为象限变换器的输入,由象限变换器完成数据的象限变换。其转换原则是:象限控制信号根据正弦信号的对称性把查表得到的数据转换为正负数据,并对于正弦信号的1、2象限数据进行加零操作,而对3、4象限的数据进行求补运算。余弦数据也同样,在1、4象限对数据进行加零操作,2、3象限数据进行求补运算。

4 仿真结果

利用上述小表结构实现的NCO可以输出多种频率信号并减少资源消耗,影响系统输出频率的因素主要是工作频率和器件性能。

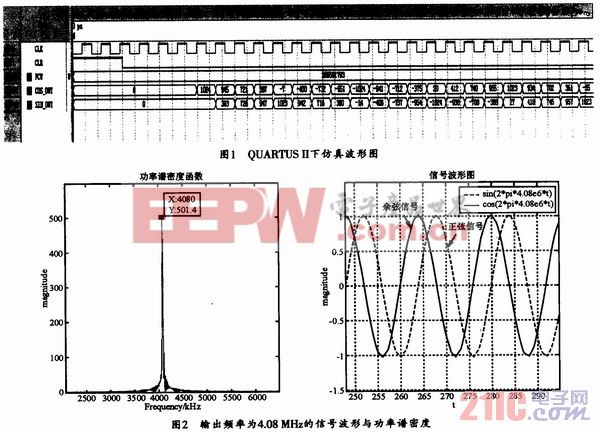

图1所示是整个NCO在QUARTUS II中的仿真波形图。

在图1所示的波形图中,CLK是时钟输入频率(为65.6 MHz),CLR为系统复位信号,相位累加器的位数L为32位,输出信号幅度位数为12位(包括符号位),相位宽度为12位,这样,由式(5)便可得到频率控制字FCW为269591793,图1中的COS_OUT与SIN_OUT是系统输出信号,频率为4.08 MHz。

由式(11)、(12)、(13)可得,此系统的信噪比和SFDR分别为74 dB和84 dB。

图2所示是将波形文件中的正弦余弦数据读入MATLAB中所显示出来的波形。

5 结束语

本文通过分析数控振荡器的实现原理和性能,给出了通过FPGA来实现NCO的具体方法,同时通过QUARTUSⅡ中的仿真验证了本设计的正确性。结果证明,用该方法设计的NCO可以输出多种频率的信号,同时也可以减少资源消耗。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码