基于ARM920T设计的SMC接口研究与PC/104总线仿真

2 EP9315(ARM920T)体系

2.1 存储器结构和地址空间

EP9315是Cirrus Logic公司生产的典型ARM 920 TDM I(Thumb,Debug,M ultiply,Em—bedded ICE macrocel1)32位哈佛结构处理器.EP9315有一个通用存储器访问接口,支持SDRAM,SRAM,ROM,及FLASH(包括N0R FLASH)等不同形式的存储器,各种存储器访问均共享数据总线DA[3l:O]和地址总线AD[Z5:o],使用统一的访问控制逻辑 。

与X86模型不同,ARM 平台只实现一个物理地址空间,在Bo0T成功后只拥有一个唯一的虚地址空间,CPU不设立专门的外设I/O指令,访问外设I/O端口和内存单元使用相同的指令.

引脚CSn[7:6]和CSn[3:O]用于存储器芯片的选通,除发生时间略有差异之外(图2),基本上可视为地址总线的高位线.

2.2 AHB总线时序和SRAM 接口

AHB(Advanced High-Speed Bus)是EP93 1 5内部920T核与存储器、DMA,存储器等设备实现高速互联的系统总线.EP9315的AHB具有完善的多主控冲突仲裁能力,其典型工作频率可达100 MH。

静态存储控制器SMC(Static Memory Controller)与920T核心通过AHB互联,支持存储器的8/16/32位访问方式.SMC最多可提供8个组,每个组均可支持SRAM,ROM,FLASH EPROM 等存储器的访问,各组可以对数据总线宽度和速度等参数独立配置.图2描述了SRAM 读操作时序.

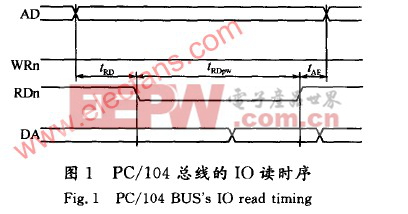

图中f删为CSn到RDn的延迟,最大值为3 ns;tDAs是RDn无效前的数据总线建立时间,最小值为12+tHcI tRDD 是RDn有效时间,典型值为t HcI K×(W ST1+ 2)。

HCLK是AHB总线的工作频率,该频率的高低直接影响系统全局性能,因此通常配置为上限100 MHz,此时相应周期£胁 为10 ns.WSTI用于控制sMc对SRAM/R0M 的访问速度,寄存器SMCBCR0—3, SMCBCR6-7 (地址0x80080000—0x8008001C)的第5-9位分别为相应各组的WST1.WST1的默认值为0xlF,即默认情况下SMC使用

最低的访问速度,显然fRDD 为330 ns,小于PC/104总线中的500 ns(图1).

3 PC/104总线实现

3.1 总线驱动

在EP9315支持的各类总线接口逻辑中,SMC提供的SRAM/ROM 时序与PC/104总线最为接近.将外部设备所需的PC端口空间和存储器空间均映射至统一的虚拟空间中即可实现访问.

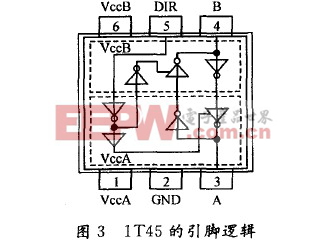

注意到PC/104总线使用标准TTL逻辑电平,而EP9315的处理器是3.3 V器件,在极端负载情况下无法保证系统稳定工作.TI的双电源总线收发器1T45,2T45,16T245等可用于实现电平转换,图3是1T45的引脚逻辑图.

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码