基于FPGA的LED大屏幕控制系统的设计实现

2 SDRAM乒乓式缓存的优化

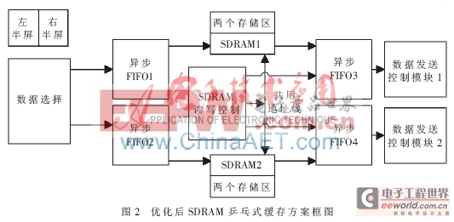

传统的基于SDRAM的乒乓式缓存方案[1,2]都存在着数据读写操作复杂或者数据结构调整局限性大的缺点。结合现有方案的优点,本文提出了图2所示的SDRAM数据缓存方案。

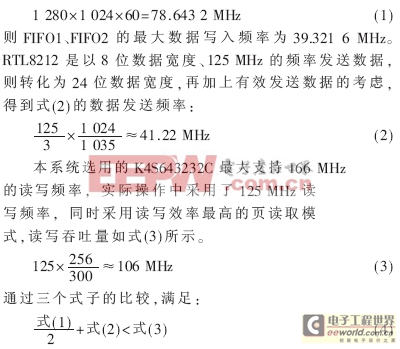

本系统的发送卡设计目标是最大支持1280×1024分辨率、60 Hz刷新率的全彩数据发送,此时的像素频率为:

即本方案满足系统数据吞吐量的要求。由于两个SDRAM中存储相同数据,具有相同格式,所以SDRAM读写模块可以同时向两个SDRAM中写入或读出显示数据,这样两块SDRAM可以共用地址线,从而节省数十个FPGA IO端口,这是本方案的一大优点。同时每块SDRAM中划分了两个区,用以存放连续的两帧图像,可以根据LED显示屏的具体要求,从SDRAM中读出显示数据,满足系统灵活性的要求。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码