基于FPGA的DDFS与DDWS两种实现方式

2 数字实现

2.1 DDFS的数字实现

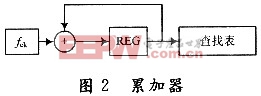

由于D/A之前都是数字部分,为了分析其原理数字控制的实现过程,参考如图2所示结构。

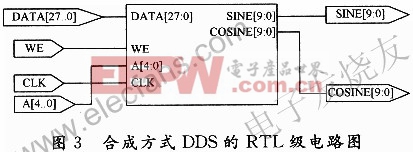

相位累加器是由一个加法器和一个寄存器构成,假设累加器位数N=6,那么000000代表0弧度,000001代表弧度,相应的000010代表(2π/64)*2弧度,111111代表(2π/64)*63弧度。若频率控制字FCW=000011,并且累加器中的初始相位为O,则经过N=21个时钟周期后形成的二进制序列为000000,000011,…,111111,对应的相位分别为O,(2π/64)*3,…,(2π/64)*63。当第22个时钟周期到来时,加法器溢出,所有位数重置为0,另一个循环周期开始。查找表可以用FPGA中BlockRAM做成,前面的二进制序列作为地址,相位对应的幅度值作为地址对应的值存储起来,这样在时钟频率的控制下通过二进制序列可从BlockRAM中读取相应的幅值,经过D/A后就为所需要的模拟波形。图3为FPGA综合后的RTL级电路图。

2.2 DDWS的数字买现

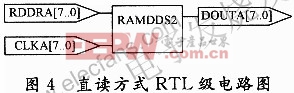

DDWS的数字实现较为简单,把通过Matlab抽样量化后的数据直接保存为.BAT数据格式,然后在FPGA中用IP核的BlockRAM生成一个ROM,把数据存储进去,这样就可以根据时钟要求输出需要的数据了。

图4为FPGA仿真后的RTL级电路图。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码