CPLD在基于PCI总线的功率模块设计中的应用

3.1 CPLD功能设计

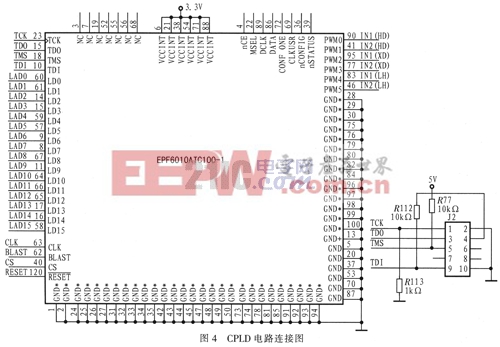

系统设计时考虑到实用和成本等因素,选用Altera公司FLEX6000系列CPLD EPF6010ATC100-1。EPF6010ATC100-1是专为大容量设计的一种低成本可编程交错式门阵列,共有16 000个可用门,1320个逻辑单元,117个I/O引脚,每个I/O引脚都有独立的三态输出使能控制。该器件采用OPEFLEX结构,采用最小的封装尺 寸并具有高性能和高布线率。器件的基本组成是逻辑单元(LE)。每个逻辑单元由一个4输入查找表、一个寄存器以及作为进位链和级连链功能的专用通道。每 10个逻辑单元组成一个逻辑阵列块(LAB),并采用SRAM构造,可通过外部EEPROM或控制器实现在线配置,便于设计者在设计初期以及设计测试过程 中对设计灵活修改,同时也能够通过在线重新配置改变其内部功能。图4为产生PWM信号的CPLD电路连接图。

CPLD功能设计思路:对电机控制时,MCU将一个16位数据写入CPLD器件的寄存器,CPLD则按照不同的数据产生相应的PWM波形。16位数据的分配如图5所示。

EPF6010ATC100-1的输入信号共有16个数据信号(LD[15:0])和4个控制信号(CLK、BLAST、CS和 RESET),16个数据信号用于接收:MCU模块发送的16位数据字。4个控制信号中,CLK为CPLD工作的时钟信号,频率可高达40 MHz,用于计数并产生准确的PWM占空比:BLAST为状态信号,低电平时表示处于数据期,此时将数据读入寄存器,等待BLAST上升沿,即该次数据访 问结束后发出

PWM信号:CS信号用于片选CPLD器件:RESET则用于对CPLD器件复位,复位后,6个输出引脚均为高阻态。

本系统设计选用的电动机PWM控制系统是双极性可逆系统,双极性驱动是指一个PWM周期中,作用于电枢两端的脉冲电压正负交替:可逆系统是指电动机可以 正反两个方向旋转,因此采用两个引脚产生PWM信号来控制电机的正反转。P1.0和P1.1、P2.0和P2.1、P3.0和P3.1设置为三组PWM信 号通道,当P1.0产生PWM波形时P1.1为低电平,此时电机正转,反之电机反转,并通过LD15控制电机运转方向。为了简化程序设计和以节省成本,根 据实际需要,设计该三组通道不同时产生PWM信号,同一时刻只产生一组PWM信号,通过LD[14:13]选择具体通道产生的PWM信 号;LD[12:6]用于给定PWM信号的占空比;LD[5:0]用于给定PWM信号频率,范围为1 kHz~63 kHz,能满足驱动电机需要。如果需要改变PWM信号的占空比、频率、方向或更换PWM通道,只需再发送一个16位数据即可足要求。

3.2 CPLD开发工具

Altera公司开发的Quartus II软件为可编程片上系统(SOPC)设计提供了一个工具齐全、功能强大的设计环境。Quartus II软件可完成设计输入、综合、布局布线、时序分析、仿真和编程等功能。根据需要选用CPLD器件系列,采用Veilog HDL语言输入方式编写控制组合逻辑代码和测试激励代码,利用Quartus II软件自带的工具分析综合代码,并进行布局布线、资源分配以及时序分析和波形仿真。Quartus II还为第三方EDA工具软件提供了友好接口,可直接在Quartus II中调用Modelsim软件进行前期的功能仿真和布局布线后的时序仿真。

4 结束语

利用CPLD技术实现了逻辑和时序的控制,简化了硬件电路设计。基于CPLD的可编程特点,可以在不改变硬件电路整体结构的情况下对设计电路进行改造、升级以及维护:并且减少了软件程序的操作指令,简化了系统结构,提高了数据处理和读取速度。

基于CPLD的PWM控制器电路结构简单,设计方便,简化了外部线路设计,节省了PCB板空间:解决了机电一体化开发平台中MCU模块与功率模块基于 PCI总线的通信,并且设计产生占空比和频率范围可调的PWM信号能满足直流电机的要求,适用于自动控制和电力电子领域。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码